当前位置:网站首页>Automatic generation of common centroid capacitance array with arbitrary capacitance ratio

Automatic generation of common centroid capacitance array with arbitrary capacitance ratio

2022-07-22 20:43:00 【Our good side^-^】

Abstract 2002

The key performance of many analog circuits is directly related to the accurate capacitance ratio . as everyone knows , By paralleling unit capacitors of the same size in the common centroid geometry , It can greatly improve the accuracy of capacitor ratio . In this paper , A general algorithm for fitting arbitrary capacitor ratio in common centroid unit capacitor array is proposed . The algorithm pays special attention to non integers and the same ratio , To minimize mismatches . A capacitance mismatch estimation method based on oxide gradient model is also introduced . It can compare different cell capacitor array assignments . The focus of the layout problem is the general routing model . Both the algorithm and the mismatch estimation method are implemented in the automatic capacitor generation tool .

research

stay [5] Five sources of system mismatches have been identified and studied . On this basis , Developed a list of general layout rules . Process gradient , For example, oxide thickness gradient , It will cause system mismatch . The direction of the gradient is a function of the chip position on the chip [6]. It is usually assumed that the gradient is represented by a linear function [1, 7]. Again , The common control capacitor arrangement helps to eliminate this error .

Most published works on capacitor mismatch , Although very limited , But it only involves the modeling of different error sources . As we all know , The best way to achieve an acceptable match between multiple capacitors with arbitrary capacitance ratio is Larger capacitors are formed by placing unit capacitors in a common centroid capacitor array [1], However, the process is still carried out on a case by case basis .

Few experiments can be found in the literature , Designed to automate this error prone and laborious process . stay [8] in , The allocation of unit capacitors is performed under two basic constraints : At least one neighbor of each unit is another unit of the same capacitor , At the same time, each capacitor must have at least one unit on either side of the array . Although this approach leads to compact arrays of arbitrary ratios , But the public center of mass placement is fully considered . Not in [9] in , The common centroid layout is considered through a special optimization algorithm 、 Symmetrical wiring and parasitic balance . however , It is limited to device pairs .

In this paper , A general algorithm for unit capacitor allocation with arbitrary capacitor ratio is introduced , The emphasis is on non integers and the same ratio . The algorithm is systematic , It is suitable for implementation in special capacitor array devices integrated in automatic layout tools . To quantify the mismatch due to oxide gradients , A method that can not only estimate the mismatch caused by oxide gradient, but also compare various array cell assignments is proposed . Last , The results are compared with those previously published [8] Comparison .

Data sets

Experimental index

The specific methods

chart 6 Shows the corresponding figure 4 The layout of the capacitor array given in . Choose horizontal or vertical routing channels , To minimize wiring area and reduce cross coupling capacitance . The wiring channel of the top plate is separated from the wiring channel of the bottom plate , To avoid additional coupling capacitance that changes the original capacitor value . Virtual capacitors surround the array . The interconnection line extends on both sides of the unit capacitor , To reduce errors caused by mask misalignment . Add holes inside the capacitor to achieve non unit ratio , At the same time, maintain a constant area perimeter ratio [11]. Routing depends on cell allocation . However , The routing line increases with the number of unit capacitors , Therefore, the increased capacitance is roughly proportional . It should be noted that ,[5] The rules given in are also respected .

D. Sayed and M. Dessouky, “Automatic generation of common-centroid capacitor arrays with arbitrary capacitor ratio,” Proceedings 2002 Design, Automation and Test in Europe Conference and Exhibition, 2002, pp. 576-580, doi: 10.1109/DATE.2002.998358.

Worth following up

- Larger capacitors are formed by placing unit capacitors in a common centroid capacitor array [1]

- [8] in , The allocation of unit capacitors is performed under two basic constraints : At least one neighbor of each unit is another unit of the same capacitor ,

- [9] in , The common centroid layout is considered through a special optimization algorithm 、 Symmetrical wiring and parasitic balance . however , It is limited to device pairs 【 a key 】

- [5] The rules given in are also respected .

边栏推荐

猜你喜欢

模拟电路中晶体管阵列的性能感知公共质心布局和布线 ALIGN

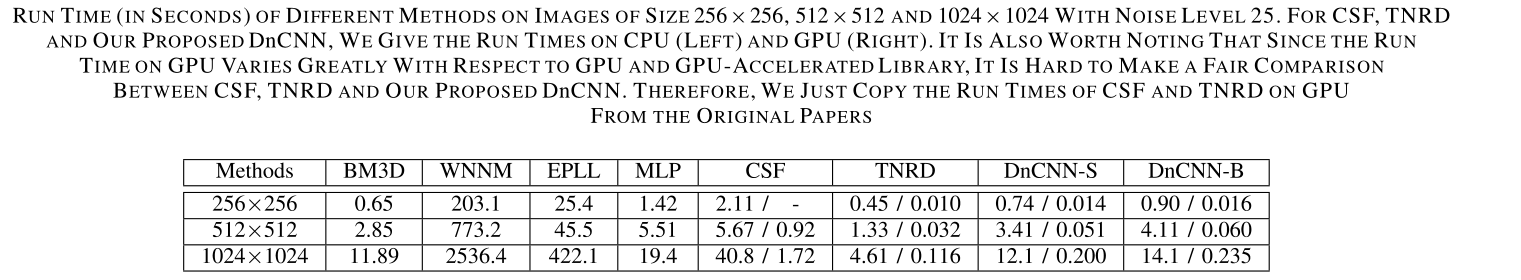

【文献阅读与想法笔记14】Beyond a Gaussian Denoiser: Residual Learning of Deep CNN for Image Denoising

【keil软件】仿真时如何使用逻辑分析仪查看波形

使用多种加权方法在 SAR ADC 中放置二进制加权电容阵列

模拟QQ登陆界面

DETR 论文精读,并解析模型结构

信号处理:<三> DFT和FFT

栈实现(C语言)

【FPGA】:ip核--Divider(除法器)

Common centroid capacitor layout generation considering device matching and parasitic minimization

随机推荐

具有非矩形布局1结构的电流镜的梯度灵敏度降低

1057 stack (30 points)

【面试:基础篇05:快速排序】

PAT-2021年冬季考试(满分)

尾插法构造链表

模拟电路中晶体管阵列的性能感知公共质心布局和布线 ALIGN

1080 graduate admission (30 points)

1030 travel plan (30 points)

具有任意电容比的共质心电容阵列的自动生成

结构体和联合体

Pytorch不同层设置不同学习率

【FPGA】:MicroBlaze的使用

1053 path of equal weight (30 points)

1053 Path of Equal Weight (30 分)

YOLO v1、v2、v3

1076 Forwards on Weibo (30 分)

[literature reading and thought notes 14] beyond a Gaussian noise: residual learning of deep CNN for image recognition

Parasitic sensing size and detailed routing of binary weighted capacitors in charge graded DAC

Intensive reading of Detr paper and analysis of model structure

适用于高密度或高精度应用的高度可配置和可扩展的螺旋电容器设计