当前位置:网站首页>FPGA skimming p2: multifunctional data processor, calculate the difference between two numbers, use generate For statement simplifies the code, uses sub modules to realize the size comparison of three

FPGA skimming p2: multifunctional data processor, calculate the difference between two numbers, use generate For statement simplifies the code, uses sub modules to realize the size comparison of three

2022-07-20 09:56:00 【Juanshi】

The topic is the programming problem of Niuke network ,part1 The link is on it , The book follows the above and is shared today part2 !

Catalog

Multifunctional data processor

Find the difference between two numbers

Use generate...for Statements simplify code

Use sub modules to compare the size of three input numbers

Use functions to realize data size conversion

Multifunctional data processor

This question mainly focuses on Signed number Programming for , There are two points to note about signed numbers :

(1) At the time of definition , Signed numbers use signed[ : ], for example output reg signed [8:0]c

(2) The highest bit of a signed number is the sign bit , by + perhaps -

`timescale 1ns/1ns

module data_select(

input clk,

input rst_n,

input signed[7:0]a,// Signed number

input signed[7:0]b,

input [1:0]select,

output reg signed [8:0]c

);

[email protected](posedge clk or negedge rst_n)begin

if(~rst_n)begin

c<=9'b0;

end

else begin

case(select)

2'd0:c<={a[7],a};// The highest bit is the sign bit

2'd1:c<={b[7],b};

2'd2:c<={a[7],a}+{b[7],b};

2'd3:c<={a[7],a}-{b[7],b};

default: c<=9'b0;

endcase

end

end

endmoduleFind the difference between two numbers

This question is in Chinese if-else Statement can be solved , The code is as follows :

module data_minus(

input clk,

input rst_n,

input [7:0]a,

input [7:0]b,

output reg [8:0]c

);

[email protected](posedge clk or negedge rst_n)begin

if(~rst_n)begin

c<=9'b0;

end

else begin

if(a>b)begin

c<=a-b;

end

else if(a<b)begin

c<=b-a;

end

end

end

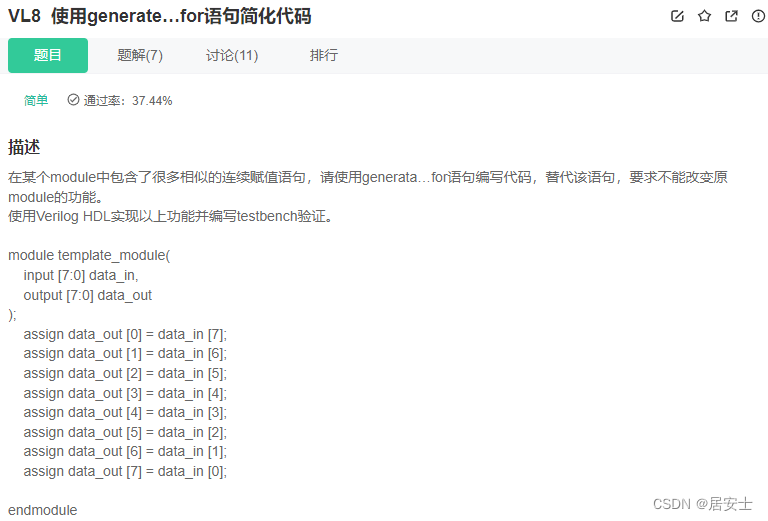

endmoduleUse generate...for Statements simplify code

This question mainly examines Verilog in genrate—for Use of statements , and c Languages are similar but different , The process is as follows :

genvar Variable ;

generate for( Initial value of variable ; Variable jump ; Variable +1)

begin:gen_ Variable

sentence ;

end

endgenerate·

Be careful :

Use generate —for Statements must be preceded by genvar Statement declaration variables

generate —for After the sentence begin: You need to add a variable ( Name doesn't matter )

generate —for It also needs to be endgenerate by way of conclusion

The code is as follows :

module gen_for_module(

input [7:0] data_in,

output [7:0] data_out

);

genvar i;

generate for(i=0;i<8;i=i+1)

begin:gen_i

assign data_out[i]=data_in[7-i];

end

endgenerate

endmoduleJust to summarize by the way for Use of statements :

integer Variable ;

for( Initial value of variable ; Variable jump ; Variable +1)

begin

sentence ;

end

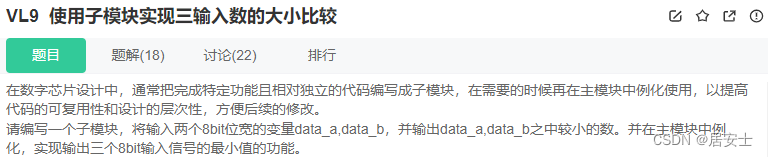

Use sub modules to compare the size of three input numbers

This question mainly examines our understanding of “ Exemplification ” Use

According to the title , We need to write a sub module by ourselves first , Realization 2 The function of minimizing the number comparison

Then instantiate 3 Secondary sub module , Input the main module 3 Number abc,a and b Smaller value than output temp1,a and c Smaller value than output temp2, And then temp1 and temp2 Compare , The minimum value is the output

This topic tells us , A sub module can be instantiated many times , Just modify the instantiation name

In the instantiation sub module ( ) The input and output in is the variable of the main module , Can change the name

The code is as follows :

// The main module compares two sub modules , Output 3 The smallest of the two values

module main_mod(

input clk,

input rst_n,

input [7:0]a,

input [7:0]b,

input [7:0]c,

output [7:0]d

);

wire [7:0] temp1;

wire [7:0] temp2;

junior_mod u1(

.clk(clk),

.rst_n(rst_n),

.a(a),

.b(b),

.c(temp1)//a And b The minimum value of comparison is temp1

);

junior_mod u2(

.clk(clk),

.rst_n(rst_n),

.a(a),

.b(c),

.c(temp2)//a And c The minimum value of comparison is remp2

);

junior_mod u3(

.clk(clk),

.rst_n(rst_n),

.a(temp1),

.b(temp2),

.c(d)//temp1 And temp2 The minimum value of comparison is d

);

endmodule

// Sub module implementation 2 Compared with

module junior_mod(

input clk,

input rst_n,

input [7:0]a,

input [7:0]b,

output [7:0]c

);

reg [7:0]c_reg;

[email protected](posedge clk or negedge rst_n )begin

if(~rst_n)begin

c_reg<=8'd0;

end

else begin

if(a>b)begin

c_reg<=b;

end

else if(b>a)begin

c_reg<=a;

end

end

end

assign c=c_reg;

endmodule

Use functions to realize data size conversion

This question examines our structural design , We need to build our own functions and tasks ,function and task Is used as follows :

Mission (task)

(1) Usually used for debugging , Or describe the behavior of the hardware

(2) It can include timing control (# Delay ,, wait)

(3) There can be input, output, and linout Parameters

(4) You can call other tasks or functions

function( Mission )

(1) Usually used to calculate , Or describe combinatorial logic

(2) Cannot include any delay ; The function simulation time is 0

(3) Contains only Input Parameter and return a result by the function name

(4) You can call other functions , But you can't call the task

This problem uses function The code is as follows :

module function_mod(

input clk,

input rst_n,

input [3:0]a,

input [3:0]b,

output [3:0]c,

output [3:0]d

);

function [3:0] begin_end;// Define the function name

input [3:0] data_in; // Define input variables

begin

begin_end[0]=data_in[3];// Size bit conversion

begin_end[1]=data_in[2];

begin_end[2]=data_in[1];

begin_end[3]=data_in[0];

end

endfunction

assign c=begin_end(a);// Call function

assign d=begin_end(b);

endmodule

边栏推荐

- Bing必应搜索用不了方法

- 使用小技巧(一)

- 二分查找 mid值溢出问题

- Vulnhub target jangow: 1.0.1

- printf的归宿-数据打印到哪儿了

- EIM总线如何测试可用性及稳定性

- Redux main knowledge learning summary

- Vulnhub target earth

- Pearson correlation coefficient and code implementation (C language +matlab)

- Interpretation of semi supervised contractual learning for label effective medical image segmentation

猜你喜欢

Allegro (cadence) export Gerber file steps

Quanzhi t507 realizes the whole process of SPI to can

The Debian system is ported with USBWiFi rtl8192eu driver and set to start automatically

Depth evaluation of Ruixin micro rk3568 development board

基于飞凌NXP i.MX6ULL的无线网络测试

皮尔逊相关系数及代码实现(C语言+MATLAB)

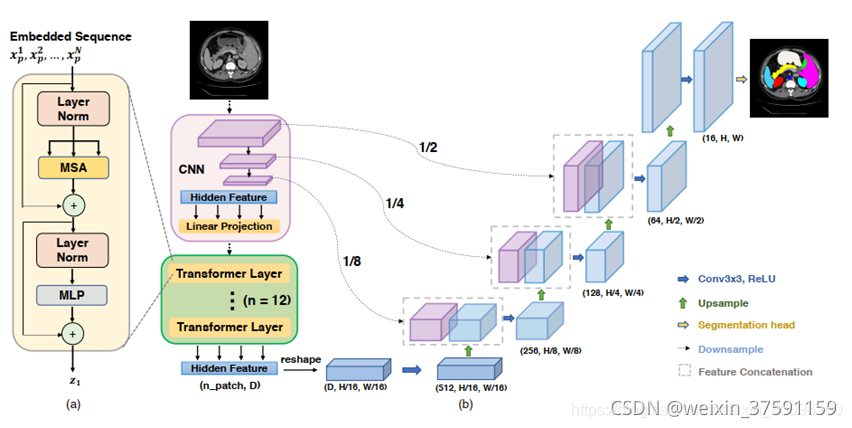

Interpretation of the paper: Transformers make strong encoders for medical image segmentation

代码审计之企业级进销存管理系统

基于定时器捕获功能的红外解码程序(NEC协议)

电脑快捷方式变白原因及解决方法——血的教训呜呜呜

随机推荐

Solution of STM32 cubeide breakpoint failure

FPGA -- detailed explanation of the principle of displaying images with VGA timing (2)

printf的归宿-数据打印到哪儿了

RS232标准DB9接口定义

基于飞凌NXP i.MX6ULL的无线网络测试

Vulnhub target goldeneye: 1

用LS1028A开发板输出PWM方波

单电源运放和双电源运放及其供电方式选择与转换的注意事项

Precautions for the selection and conversion of single power supply operational amplifier and dual power supply operational amplifier and their power supply mode

瑞萨G2L核心板及开发板上手评测

E2EC: An End-to-End Contour-based Method for High-Quality High-Speed Instance Segmentation

How to understand the freezing network parameters in the mindscore official website tutorial? Can you explain it?

基于瑞芯微3568核心板实现的智能网关

Allegro cannot display drill legend information when adding drill legend

Quanzhi t507 realizes the whole process of SPI to can

UltraEdit自动换行/制表符设置

Interpretation of semi supervised semantic segmentation with error localization network

Verilog语言中按位取反和逻辑取反的区别

Interpretation of semi supervised contractual learning for label effective medical image segmentation

全志 T507实现SPI转CAN 全过程