当前位置:网站首页>Leetcode:2. 两数相加【大数加法+模拟进位】

Leetcode:2. 两数相加【大数加法+模拟进位】

2022-07-19 05:15:00 【星空皓月】

题目描述

给你两个 非空 的链表,表示两个非负的整数。它们每位数字都是按照 逆序 的方式存储的,并且每个节点只能存储 一位 数字。

请你将两个数相加,并以相同形式返回一个表示和的链表。

你可以假设除了数字 0 之外,这两个数都不会以 0 开头。

输入与输出

输入:l1 = [2,4,3], l2 = [5,6,4]

输出:[7,0,8]

解释:342 + 465 = 807.

提示

- 每个链表中的节点数在范围 [1, 100] 内

- 0 <= Node.val <= 9

- 题目数据保证列表表示的数字不含前导零

思路

模拟加法操作,将对应位置相加,如果大于10,则将其进位,同时需要注意最后一次进位操作,例如99+1。

时间复杂度为O(max(len(l1), len(l2)))

AC代码(C++)

/** * Definition for singly-linked list. * struct ListNode { * int val; * ListNode *next; * ListNode() : val(0), next(nullptr) {} * ListNode(int x) : val(x), next(nullptr) {} * ListNode(int x, ListNode *next) : val(x), next(next) {} * }; */

class Solution {

public:

ListNode* addTwoNumbers(ListNode* l1, ListNode* l2) {

ListNode *head=nullptr, *tail=nullptr;

int temp = 0; // 表示是否有进位值

while(l1 || l2) {

int n1 = l1 ? l1->val : 0; // 当前每一位的值

int n2 = l2 ? l2->val : 0; // 当前每一位的值

int sum = n1 + n2 + temp; // 每一位的值相加,同时加上上一位是否有进位值

if (!head) {

head = tail = new ListNode(sum % 10); // 将这个值放到一个新的链表中

} else {

tail->next = new ListNode(sum % 10); // 如果链表不为空,则继续添加该节点,同时尾节点向后移一位

tail = tail->next;

}

temp = sum / 10; // 表示正在相加的位置是否可进位

if (l1) {

l1 = l1->next;

}

if (l2) {

l2 = l2->next;

}

}

// 最后看是否有进位,如果有,则加上,例如99 + 1

if(temp>0) {

tail->next = new ListNode(temp);

}

return head;

}

};

边栏推荐

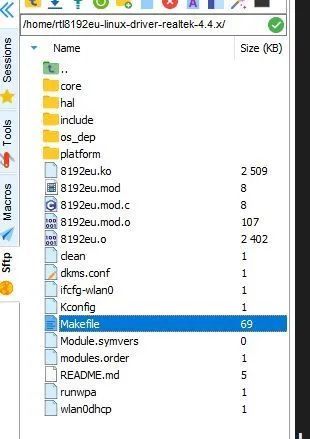

- i.MX8MP开发板移植USBWIFI RTL8192EU驱动

- Xilinx FPGA关键资源评估

- Hard core strength! Feiling Ti Sitara am62x series-335x classic continuation

- 基于定时器捕获功能的红外解码程序(NEC协议)

- ZYNQ ARM核之SCU

- vivado2018.2报错及解决方法记录

- TypeScript 中类型 any,void,unknown,never之间的区别

- Log access development with one person per day and nine people per day -- project development practice based on instruction set Internet of things operating system

- Many new features of ktor2.0 were thought of a year ago and have been implemented in the project

- Allegro (cadence) export Gerber file steps

猜你喜欢

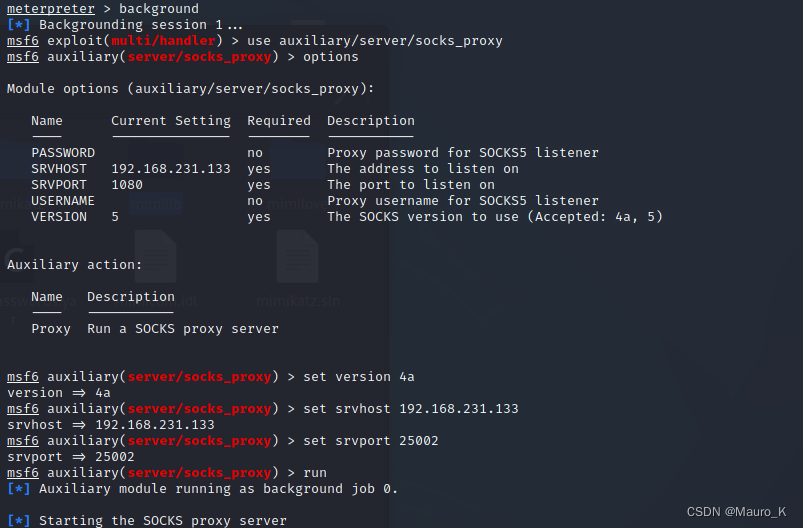

Connaissance de la technologie des tunnels d'infiltration Intranet

The end result of printf - where is the data printed

UltraEdit line break / tab settings

Allegro (cadence) export Gerber file steps

![[Lora & nb IOT] current situation analysis](/img/d1/eaddcac26f9800dbe5f74190521589.png)

[Lora & nb IOT] current situation analysis

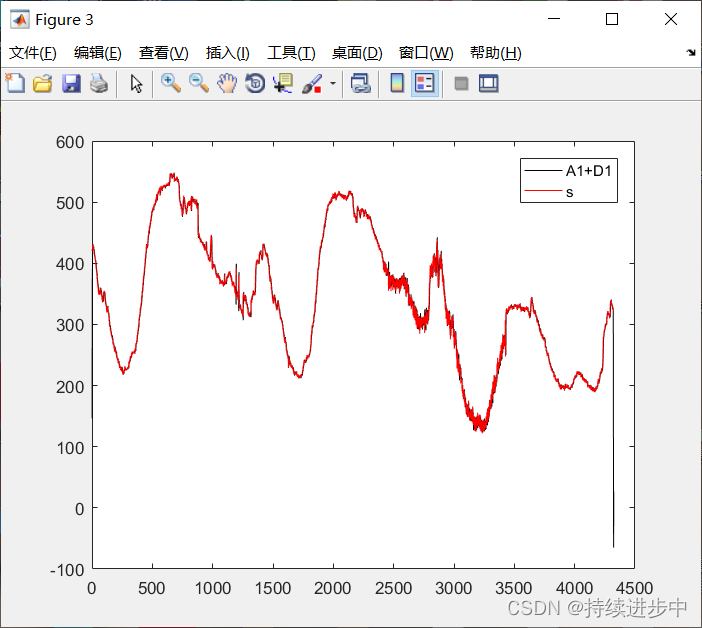

Program verification of one-dimensional wavelet transform based on cyclic convolution (C language)

First hand evaluation of Reza g2l core board and development board

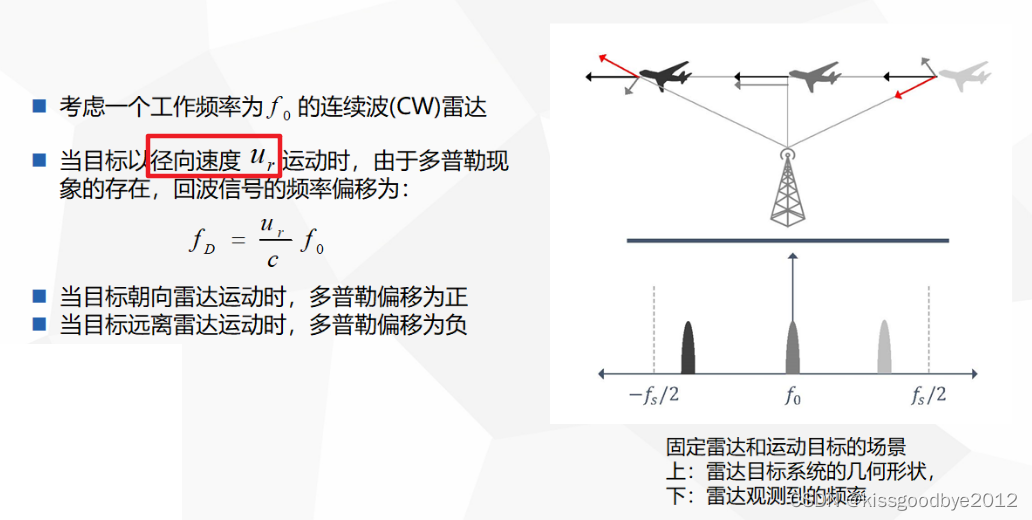

雷达基础系列文章之五:雷达调制样式的功能

The Debian system is ported with USBWiFi rtl8192eu driver and set to start automatically

Least square linear fitting and its code implementation (C language)

随机推荐

FPM生成封装时关联Allegro打开后无法生成封装问题解决办法

PCL基本操作大全

FPGA - encapsulation and call of IP core (vivado)

vulnhub 靶机 GOLDENEYE: 1

Bing Bing search doesn't work

【Vscode配置Markdown环境】亲测好用~

Log access development with one person per day and nine people per day -- project development practice based on instruction set Internet of things operating system

Understanding of arm interrupt priority

2021-09-30

常见设备默认口令

How to set the oil on the through hole cover when exporting the Gerber file of PCB

How to put a "platform" into a small box? (I) scheme comparison

正则表达式的设计

Chrome developer tool shortcut key reference to improve development efficiency

代码审计之企业级进销存管理系统

SCU of zynq ARM core

(data and electricity) summary of various triggers - FPGA octet (1)

[vscade configuration markdown environment] user friendly~

Definition, calculation method and relationship among linear convolution, cyclic convolution and periodic convolution

FPGA network port implementation and detailed explanation (2)