当前位置:网站首页>Chapter V central processing unit

Chapter V central processing unit

2022-07-21 17:37:00 【codefan※】

a central processor

CPU The function and basic structure of

CPU The function of

- The central processing unit is composed of arithmetic unit and controller .

- Arithmetic unit : Process the data

- controller : Be responsible for coordinating and controlling the instruction sequence of computer components to execute programs ( Take command 、 Analysis instructions 、 Execution instruction )

- function : Command control 、 Operational control 、 time control 、 The data processing 、 Interrupt handling

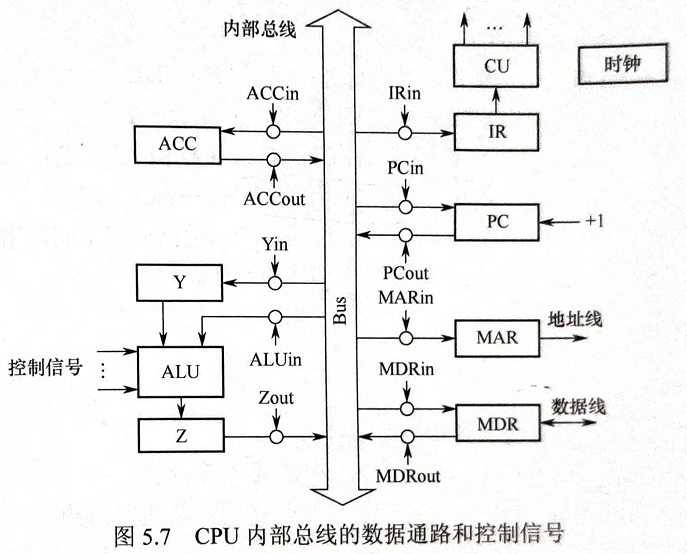

CPU Basic structure

- Arithmetic unit

| form | function |

|---|---|

| Arithmetic logic unit ALU | Do arithmetic / Logical operations |

| Temporary register | Temporarily store data read from main memory , Transparent to application meta |

| Accumulation register ACC | The staging ALU Operation result information , It can be used as an input of addition operation |

| General register group | Used to store operands |

| Program status word register PSW | All kinds of state information established by the result of arithmetic logic operation instruction or test instruction are retained |

| Shifter | Shift the operand or operation result |

| Counter CT | Controls the number of steps in multiplication and division |

- controller

| form | function |

|---|---|

| Program counter PC | Used to indicate the location of the next instruction in main memory |

| Instruction register IR | It is used to save the currently executing instruction |

| Instruction decoder | |

| Memory address register MAR | The address used to store the main memory unit to be accessed |

| Memory data register MDR | Used to store information written to or read from main memory |

| Sequential systems | Used to generate all kinds of timing signals , They all consist of a unified clock CLOCK Divide the frequency to get |

| Micromanipulation signal generator |

Instruction execution process

Instruction cycle

| Concept | explain |

|---|---|

| Instruction cycle | CPU The time taken to fetch and execute an instruction from main memory , It is often expressed by several machine cycles |

| Machine cycle | Contains several clock cycles |

| Clock cycle | CPU The most basic unit of operation |

A complete instruction cycle should include values 、 Inter site 、 Execution and interruption 4 A cycle .

- The addressing period is Take command

- The inter address period is Take a valid address

- The execution cycle is Fetching operands

- The interruption period is Save program breakpoints

Instruction cycle data flow

Take the period : according to PC Take the instruction code from the main memory and store it in IR in

- PC → MAR → Address bus → Main memory

- CU → Control bus → Main memory

- Main memory → data bus → MDR → IR

- CU → PC

Interval period : Fetch the valid address of the operand

- IR → MAR → Address bus → Main memory

- CU → Control bus → Main memory

- Main memory → data bus → MDR

Execution cycle : Fetching operands , And according to IR The opcode of the instruction word in passes ALU Operations produce execution results

Interrupt cycle : Save breakpoints , Send interrupt vector , Processing interrupt requests

Instruction execution scheme

Single instruction cycle

- Choose the same execution time for all instructions

- Between instructions Serial execution

- The instruction cycle depends on the execution time of the instruction with the longest execution time

- It will reduce the running speed of the whole system

Multiple instruction cycles

- Choose different execution steps for different types of instructions

- Between instructions Serial execution

- Need more complex hardware design

Pipeline solution

- Instructions can Parallel execution The plan

Function and basic structure of data path

The function of data path

The path through which data is transferred between features is called Data access

The function of data path is Realization CPU Internal arithmetic unit and register and data exchange between registers

The basic structure of data path

| The basic structure | Advantages and disadvantages |

|---|---|

| CPU Internal single bus mode | Simple structure , Easy to implement , There are many conflicts in data transmission , Low performance |

| CPU Internal three bus mode | Different data can be transmitted on multiple buses at the same time |

| Dedicated data path mode | There is basically no data conflict , Higher performance , But the amount of hardware is large , It's not easy to achieve |

- An internal bus is the same component

- System bus refers to the components of the same computer system

- Data transfer between registers

// With PC For example

PC → Bus Pcount It works ,PC Content delivery bus

Bus → MAR MARin It works , The bus content is sent to MAR

- Main memory and CPU Data transfer between

// With CPU Take reading instructions from main memory as an example

PC → Bus → MAR PCout and MARin It works

1 → R CU Issue a read command

MEM(MAR) → MDR MDRin It works

MDR → Bus → IR MDRout and IRin It works

- To perform arithmetic or logical operations

// Take addition as an example

Ad(IR) → Bus → MAR MDRout and MARin It works

1 → R CU Issue a read command

MEM → cable → MDR

MDR → Bus → Y

(ACC) → (Y) → Z

Z → ACC

notes : Understand together with the above figure

Function and working principle of the controller

Structure and function of the controller

边栏推荐

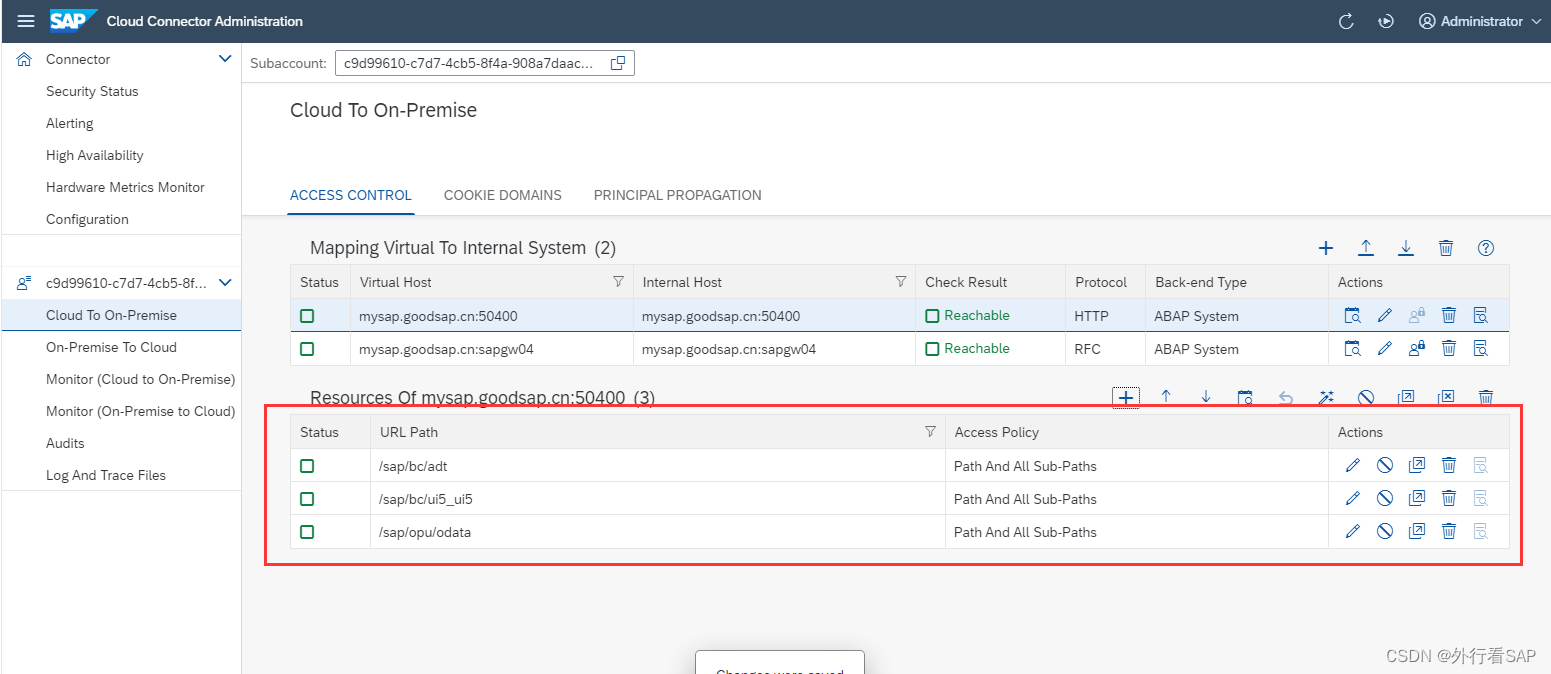

- SAP Fiori topic 2: using webide to build Fiori with navigation bar

- PHP FPM custom ZABBIX monitoring

- 华为无线设备配置基于ACL的报文过滤

- 下游任务(downstream task)含义

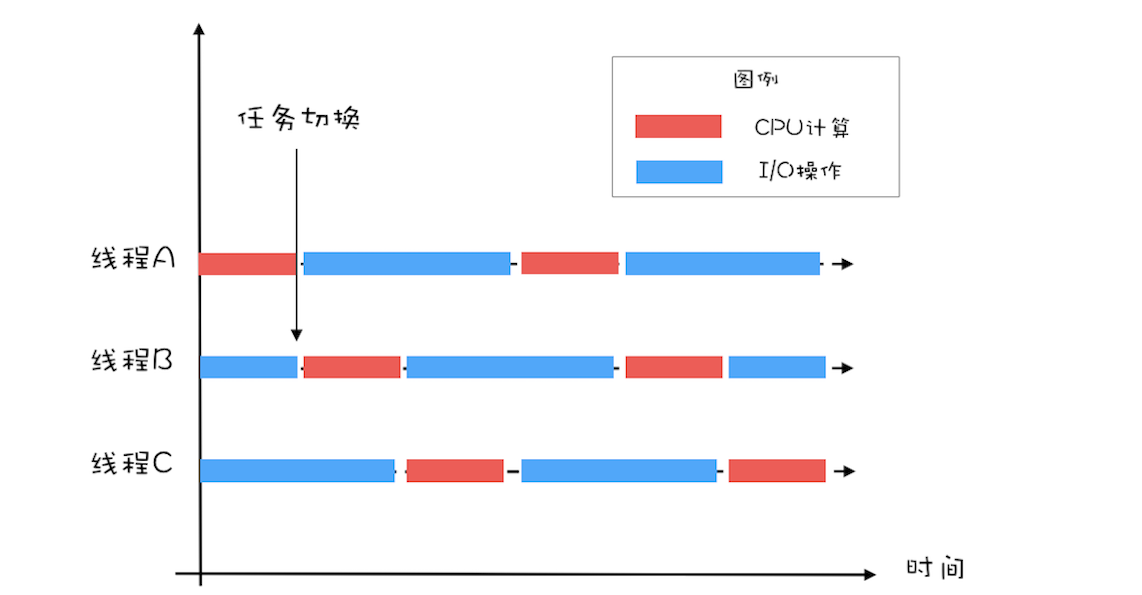

- 实践-创建多少线程合适

- 如何用度量数据驱动代码评审的改善

- Huawei wireless devices are configured with non fast roaming between APs of different service VLANs

- JS--循环--猜数字(生成随机数存在小数Math.random)

- Traverse the pictures of folders and subfolders, use OpenCV to change the size and save to a folder

- Find in 2D array

猜你喜欢

IP第十一天笔记

模块学习(五)——矩阵键盘

SAP Fiori topic 2: using webide to build Fiori with navigation bar

华为无线设备配置Airtime调度

C#(三十九)之关于string的一些函数

Practice - how many threads are appropriate to create

Kubernetes apiserver, etcd, controller manager, scheduler high availability principle

带你认识一下数仓的分区自动管理

Junda technology - Mobus to SNMP network monitoring terminal

Huawei wireless device configuration traffic supervision

随机推荐

The difference between memory overflow and memory leak

【机器学习】如何在训练过程中挑选比较好的模型保存(pytorch)

Resolved module not found: error: can't resolve 'core JS / FN / reflect' in

C#(三十四)之坐标变换

第五章 中央处理器

如何用度量数据驱动代码评审的改善

Latest microservice component selection

Swift 中风味各异的依赖注入

php-fpm自定义zabbix监控

MD编辑器 - Typora

Regression prediction analysis of jujube genetics based on support vector machine

How to use measurement data to drive the improvement of code review

两地三中心部署

每周推荐短视频:物联网开发提出更大挑战?

C#(三十七)之基于流的文件操作(FileStream)

华为无线设备配置同一业务VLAN的AP间快速漫游

Power BI----让报表更美观之切片器

线程间有哪些资源是不可以共享的?

IP day 11 notes

被鱼粉直呼小鱼牛逼的代码,来看ROS2如何进行点云PCL处理(订阅、转换、保存)