当前位置:网站首页>【Verilog数字系统设计(夏宇闻)----Verilog的基础知识2】

【Verilog数字系统设计(夏宇闻)----Verilog的基础知识2】

2022-07-20 07:27:00 【周猿猿】

Verilog数字系统设计(夏宇闻)----Verilog的基础知识2

采用硬件描述语言(Verilog HDL)的设计流程简介

自顶向下(Top_Down)设计的基本概念

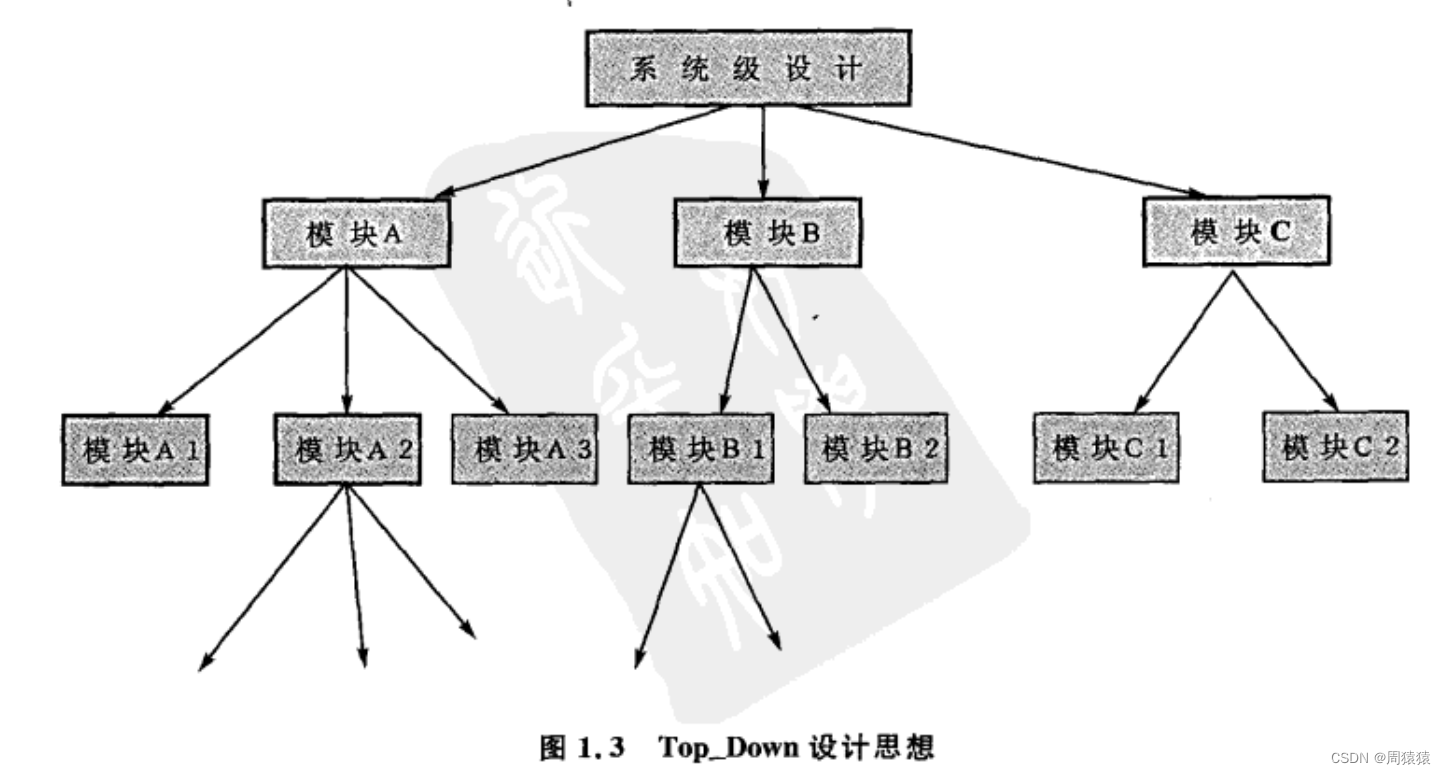

现代集成电路制造工艺技术的改进,使得在一个芯片上集成数十万乃至数于万个器件成为可能 。 但很难设想仅由一个设计师独立设计如此大规模的电路而不出现错误。 利用层次化、结构化的设计方法,一个完整的硬件设计任务首先由总设计师(Architect)划分为若干个可操作的模块,编制出相应的模型(行为的或结构的),通过仿真加以验证后,再把这些模块分配给下一层的设计师。 这就允许多个设计者同时设计一个硬件系统中的不同模块,其中每个设计者负责自己所承担的部分;而由上一层设计师对其下层设计者完成的设计用行为级上层模块对其所做的设计进行验证。 为了提高设计质量,如果其中有一部分模块可由商业渠道得到, 用户可以购买它们的知识产权的使用权(IP核的重用),以节省时间和开发经费,图1. 3为自顶向下 (Top-Down)的示意图,以设计树的形式绘出。

自顶向下的设计(即Top_Down设计)是从系统级开始 ,把系统划分为基本单元,然后再把每个基本单元划分为下一层次的基本单元 ,一直这样做下去 ,直到可以直接用EDA元件库中的基本元件来实现为止 。

对于设计开发整机电子产品的单位和个人来说,新产品的开发总是从系统设计入手 ,先进行方案的总体论证、功能描述、任务和指标的分配。 随着系统变得复杂和庞大 ,特别需要在样机问世之前,对产品的全貌有一定的预见性 。 目前,EDA技术的发展使得设计师有可能实现真正的自顶向下的设计。

层次管理的基本概念

复杂数字逻辑电路和系统的层次化、结构化设计隐含着对系统硬件设计方案的逐次分解。在设计过程中的任意层次,至少得有一种形式来描述硬件。 硬件的描述特别是行为描述通常称为行为建模 。 在集成电路设计的每一层次,硬件可以分为一些模块 ,该层次的硬件结构由这些模块的互联描述,该层次的硬件的行为由这些模块的行为描述。 这些模块称为该层次的基本单元。 而该层次的基本单元又由下一层次的基本单元互联而成。 如此下去 ,完整的硬件设计就可以由图1. 3所示的设计树描述。 在这个设计树上,节点对应着该层次上基本单元的行为描述,树枝对应着基本单元的结构分解。 在不同的层次都可以进行仿真以对设计思想进行验证。 EDA工具提供了有效的手段来管理错综复杂的层次,即可以很方便地查看某一层次某模块的源代码或电路图以改正仿真时发现的错误。

具体模块的设计编译和仿真的过程

在不同的层次做具体模块的设计所用的方法也有所不同,在高层次上往往编写一些行为级的模块通过仿真加以验证,其主要目的是系统性能的总体考虑和各模块的指标分配,并非具体电路的实现, 因而综合及其以后的步骤往往不需进行。 而当设计的层次比较接近底层时,行为描述往往需要用电路逻辑来实现 。 这时的模块不仅需要通过仿真加以验证,还需进行综合、优化、布线和后仿真。 总之具体电路是从底向上逐步实现的。 EDA工具往往不仅支持HDL描述也支持电路图输入,有效地利用这两种方法是提高设计效率的办法之一。 图1. 4所示的流程图简要地说明了模块的编译和测试过程。 从图中可以看出,模块设计流程主要由两大主要功能部分组成:

从图中可以看出,模块设计流程主要由两大主要功能部分组成:

(1) 设计开发 即从编写设计文件—>综合到布局布线---->电路生成这样一系列步骤。

(2) 设计验证 也就是进行各种仿真的一系列步骤,如果在仿真过程中发现问题就返回设计输入进行修改。

具体工艺器件的优化、映像和布线布局

由于各种ASIC和FPGA器件的工艺各不相同 , 因而当用不同厂家的不同器件来实现已验证的逻辑网表(EDIF文件)时 , 就需要不同的基本单元库与布线延迟模型与之对应,才能进行优化、映像和布局布线 ,以及布局布线后准确的仿真验证。 基本单元库与布线延迟模型由熟悉本厂工艺的工程师提供,再由EDA厂商的工程师编入相应的处理程序,而逻辑电路设计师只需用一文件说明所用的工艺器件和约束条件,EDA工具就会自动地根据这一文件选择相应的库和模型进行准确的处理,从而大大提高设计效率。

边栏推荐

猜你喜欢

![[learning notes] agc016](/img/aa/3c3f2360e781808696032814ccbc9b.png)

[learning notes] agc016

svn 的tag,分支管理,merge合并冲突

The difference between copy and copy in XMIND

MYSQL插入中文出错的解决办法

unicode 编码 输出12生肖表情图片

Jenkins uses the uploaded file parameter as a parameter

不用线段树,一个思路解决所有我的日程安排表问题

The LAAS protocol of defi 2.0 is the key to revitalizing the development of defi track

Program environment and pretreatment

Okaleido或杀出NFT重围,你看好它吗?

随机推荐

10 talk about ThreadLocal

go 原子操作

Leetcode力扣题解 - 30.串联所有单词的子串

“元宇宙”里打工还很远?“捏脸师”就在身边

SQLite memory mode save

C reflection and factory mode

Redis实现秒杀系统

每日三题 7.16

Okaleido或杀出NFT重围,你看好它吗?

The difference between copy and copy in XMIND

Daily question 1: specified interval reversal in the linked list

Jmeter线程如何顺序执行--测试计划配置

Apprentissage autojs - jeux de pièces

Jenkins uses the uploaded file parameter as a parameter

[jzof-03] repeated numbers in the array

Jmeter如何取cookie Jsession

[detailed tutorial] a thorough article on mongodb aggregation query

力扣 745. 前缀和后缀搜索

MySQL索引与事务

QT notes - customized flow layout qflowlayout