当前位置:网站首页>Verilog grammar basics HDL bits training 03

Verilog grammar basics HDL bits training 03

2022-07-21 19:30:00 【Nanyou school slag】

List of articles

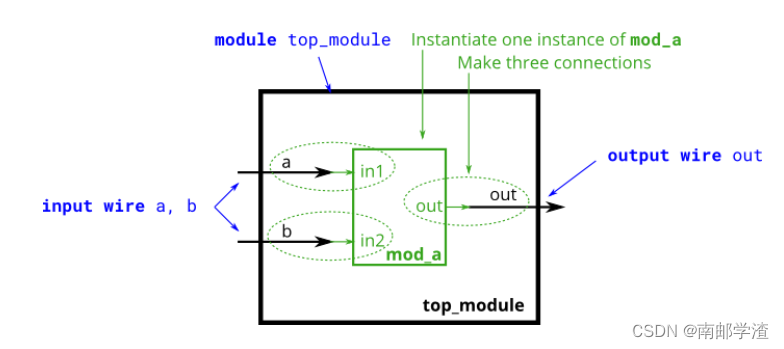

One 、Modules:Modules

Instantiate the module inside the code , This is particularly common in top-level file code

- RTL Code

module top_module ( input a, input b, output out );

mod_a instance2 (

.out(out),

.in1(a),

.in2(b)

);

endmodule

- Simulation oscillogram

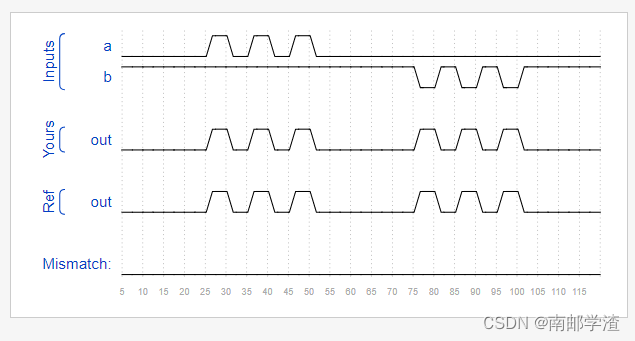

Two 、Module:conneting ports by position

- RTL Code

module top_module (

input a,

input b,

input c,

input d,

output out1,

output out2

);

mod_a mod_a_inst( out1, out2, a, b, c, d );

endmodule

- Simulation oscillogram

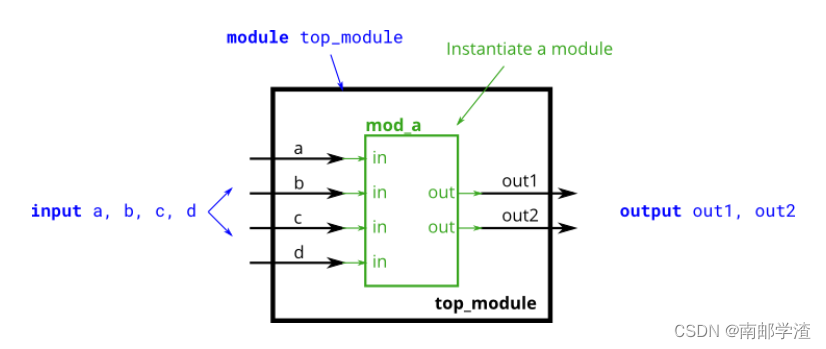

3、 ... and 、Modules:Connecting ports by name

- RTL Code

module top_module (

input a,

input b,

input c,

input d,

output out1,

output out2

);

mod_a mod_a_inst(

.out1(out1),

.out2(out2),

.in1(a),

.in2(b),

.in3(c),

.in4(d)

);

endmodule

- Simulation oscillogram

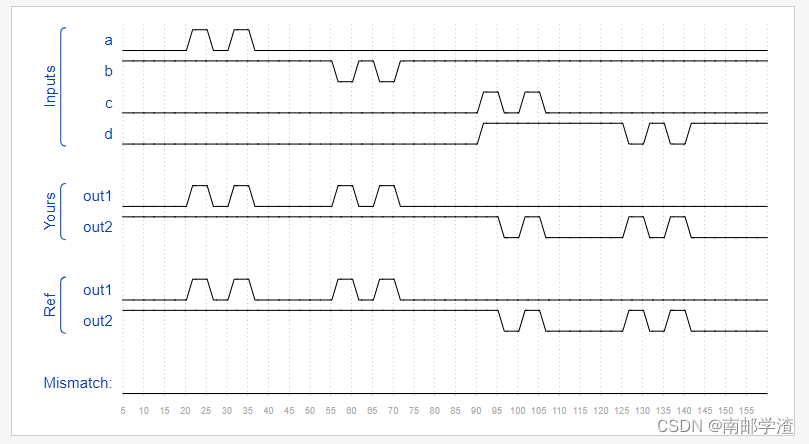

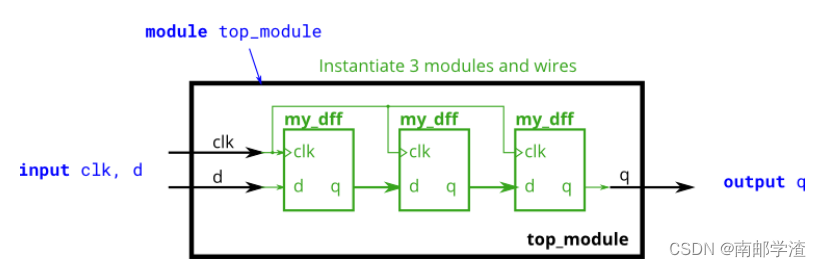

Four 、Modules:Three modules

Instantiate three modules , Pay attention to the connection of ports

- RTL Code

module top_module ( input clk, input d, output q );

wire q1,q2;

my_dff my_dff_inst1(

.clk(clk),

.d(d),

.q(q1)

);

my_dff my_dff_inst2(

.clk(clk),

.d(q1),

.q(q2)

);

my_dff my_dff_inst3(

.clk(clk),

.d(q2),

.q(q)

);

endmodule

- Simulation oscillogram

5、 ... and 、Modules:Modules and vectors

Instantiate three modules , And use always Block and case Statement to select output

- RTL Code

module top_module (

input clk,

input [7:0] d,

input [1:0] sel,

output [7:0] q

);

wire [7:0]q1;

wire [7:0]q2;

wire [7:0]q3;

my_dff8 my_dff_inst1(

.clk(clk),

.d(d),

.q(q1)

);

my_dff8 my_dff_inst2(

.clk(clk),

.d(q1),

.q(q2)

);

my_dff8 my_dff_inst3(

.clk(clk),

.d(q2),

.q(q3)

);

always @(*)

case(sel)

2'b00:q = d;

2'b01:q = q1;

2'b10:q = q2;

2'b11:q = q3;

endcase

endmodule

- Simulation oscillogram

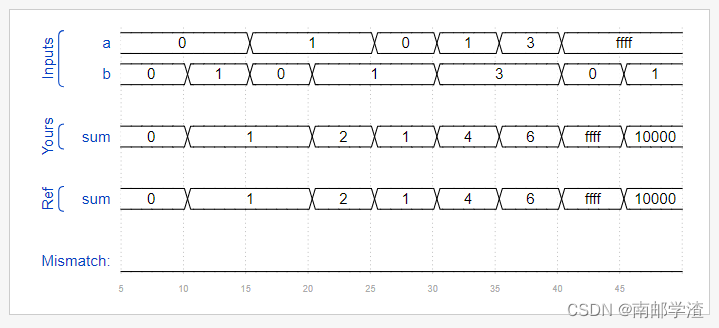

6、 ... and 、Modules:Adder1

- RTL Code

module top_module(

input [31:0] a,

input [31:0] b,

output [31:0] sum

);

wire cin;

wire [15:0]a1,a2,b1,b2;

wire [15:0]sum1;

wire [15:0]sum2;

wire cout;

assign a1 = a[15:0];

assign a2 = a[31:16];

assign b1 = b[15:0];

assign b2 = b[31:16];

add16 add16_inst1(

.a(a1),

.b(b1),

.cin(cin),

.sum(sum1),

.cout(cout)

);

add16 add16_inst2(

.a(a2),

.b(b2),

.cin(cout),

.sum(sum2),

.cout()

);

assign sum[15:0] = sum1;

assign sum[31:16] = sum2;

endmodule

- Simulation oscillogram

7、 ... and 、Modules:Adder2

- RTL Code

module top_module (

input [31:0] a,

input [31:0] b,

output [31:0] sum

);//

wire [15:0]sum1;

wire [15:0]sum2;

wire cout;

add16 addr16_inst1(

.a(a[15:0]),

.b(b[15:0]),

.cin(1'b0),

.sum(sum1),

.cout(cout)

);

add16 addr16_inst2(

.a(a[31:16]),

.b(b[31:16]),

.cin(cout),

.sum(sum2),

.cout()

);

assign sum = {

sum2,sum1};

endmodule

module add1 ( input a, input b, input cin, output sum, output cout );

assign sum = a^b^cin;

assign cout = a&b | a&cin |b&cin;

endmodule

- Simulation oscillogram

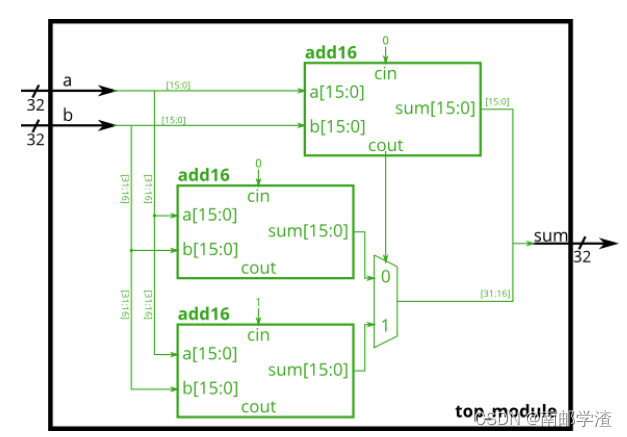

8、 ... and 、Modules:Carry-select addr

Selective output , use case Statements and two choice judgment statements are ok

- RTL Code

module top_module(

input [31:0] a,

input [31:0] b,

output [31:0] sum

);

wire cin;

wire [15:0]sum1;

wire [15:0]sum2;

wire [15:0]sum3;

wire cout;

add16 add16_inst1(

.a(a[15:0]),

.b(b[15:0]),

.cin(1'b0),

.sum(sum1),

.cout(cout)

);

add16 add16_inst2(

.a(a[31:16]),

.b(b[31:16]),

.cin(1'b0),

.sum(sum2),

.cout()

);

add16 add16_inst3(

.a(a[31:16]),

.b(b[31:16]),

.cin(1'b1),

.sum(sum3),

.cout()

);

assign sum = (!cout)? {

sum2,sum1}:{

sum3,sum1};

endmodule

- Simulation oscillogram

Nine 、Modules:Adder-subtractor

- RTL Code

module top_module(

input [31:0] a,

input [31:0] b,

input sub,

output [31:0] sum

);

wire [15:0]sum1;

wire [15:0]sum2;

wire cout;

wire [31:0]b_s;

add16 addr16_inst1(

.a(a[15:0]),

.b(b_s[15:0]),

.cin(sub),

.sum(sum1),

.cout(cout)

);

add16 addr16_inst2(

.a(a[31:16]),

.b(b_s[31:16]),

.cin(cout),

.sum(sum2),

.cout()

);

assign b_s = b ^ {

32{

sub}};

assign sum = {

sum2,sum1};

endmodule

- Simulation oscillogram

边栏推荐

- Differences between functions, methods and interfaces

- The reason why "typeerror: 'STR' object does not support item assignment" appears

- Software testing interview question: software testing is divided into several stages. What are the testing strategies and requirements for each stage?

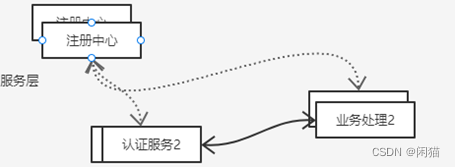

- 分布式.数据库架构

- NFS share

- Software test interview question: describe the complete process of a test activity in detail. (for reference, this answer is mainly the practice of waterfall model)

- 05 regular expression syntax

- "PHP implementation of Domain Driven Design" - integration context [reprint]

- Metahuman face shader summary

- 其他正则验证规则web launch app

猜你喜欢

MYSQL08_ Overview of sub query, single row, multi row, related sub query

四种bean拷贝工具对比

SAP smartforms print failure message type: ssfcomposer message number: 601 (currency and number field setting reference and format)

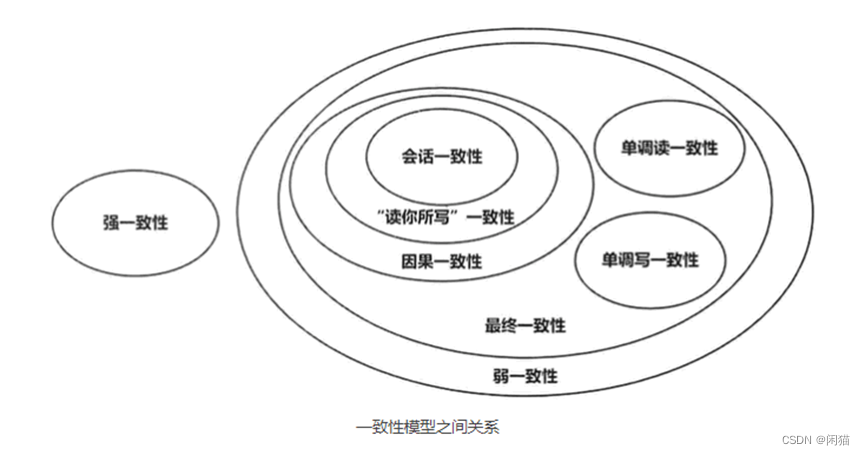

分布式.BASE理论

使用MogDB Operator在Kubernetes上部署MogDB集群(MogDB Stack)

分布式.高并发&高可用

![[qt primer] Application of window classes](/img/44/4fd62fd2e4e8115ef00e456e382de2.png)

[qt primer] Application of window classes

紫杉醇联合2-甲氧基雌二醇的白蛋白纳米粒/荜茇酰胺白蛋白纳米粒的研究制备

Pytorch deep learning practice lesson 2 / assignment (linear model)

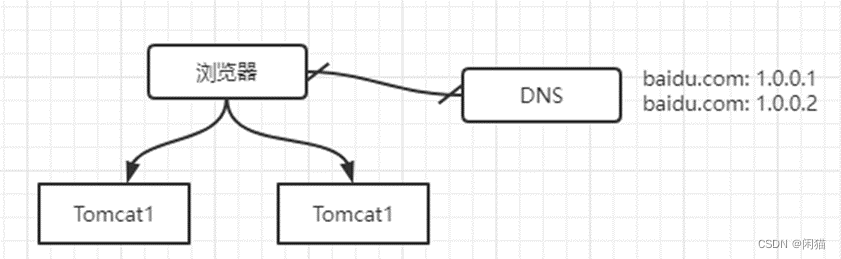

Distributed load balancing

随机推荐

Distributed Capacity evaluation

4. Custom data source of security

Software test interview question: in your previous work, what did a software defect (or bug) record contain? How to submit high-quality software bug records?

MYSQL07_ Get date function, aggregate function, string function

TiDB 分布式批量解决方案

05 regular expression syntax

分布式.容量评估

How to realize the data structure of nested tables in SQL

Don't want to wake up because it's delicious

Introduction to ESP privilege isolation mechanism

分布式.BASE理论

Distributed High concurrency & high availability

Recommended collection | practical operation, data console selection example

Web APIs DOM page special effects element size and position

打造高性能应用,持续优化用户体验

分布式.达到什么指标才算高并发

程序员第一课“hello word”,你知道网工第一课吗?

[QT入门篇]信号槽机制

SAP IDOC教程:定义,结构,类型,格式和表格-019

QT(37)-mosquitto-MQTT客户端