当前位置:网站首页>[hdlbits skimming] Verilog language -- basics

[hdlbits skimming] Verilog language -- basics

2022-07-21 05:58:00 【Linest-5】

Catalog

Write it at the front

HDLBits As Verilog Brush question website , It is very suitable for beginners to practice , You can not only learn basic grammar , You can also make the code you write more intuitive , Directly mapped to the circuit , Therefore, during this period, I will take some time every week to brush the title of this website , Use a blog to record your experience of writing questions .

Because the topics in the previous sections are relatively basic , So only show the result code and simulation waveform , Copy the translation part of the title browser for each question , Some translations are poor , The specific details will not be repeated .

Basics

Simple wire

Create a module with one input and one output , It behaves like a wire .

Different from physical wires ,Verilog Wire in ( And other signals ) yes Directional . This means that information flows in only one direction , from ( It's usually a ) Source To Receiver ( Sources are often referred to as will values drive To the wire The driver ). stay Verilog“ Continuous distribution ”() in , The value of the right signal is driven to the wire on the left . The assignment is “ Successive ”, Because even if the value on the right changes , The assignment will continue . Continuous allocation is not a one-time event .

The port on the module also has one direction ( Usually input or output ). The input port consists of objects outside the module drive , And the output port drive Something external . When viewing from inside the module , Input port is driver or source , The output port is the receiver .

module top_module(

input in,

output out

);

assign out = in;

endmoduleSimulation waveform

Four wires

A potential source of confusion that may need to be clarified now : The green arrow here indicates the wire Between Connect , But it's not a wire . Module itself already The statement 7 A wire ( Name it a、b、c、w、x、y and z). This is because , Unless otherwise stated , Otherwise, the declaration actually declares a wire . Writing and identical . therefore , These statements are not creating wires , But in what already exists 7 Create a connection between wires .

module top_module (

input a,

input b,

input c,

output w,

output x,

output y,

output z

);

assign w = a;

assign x = b;

assign y = b;

assign z = c;

endmoduleSimulation waveform

Inverter

Create an implementation NOT Door module .

This circuit is similar to a line , But slightly different . When connecting from wire to wire , We will realize inverter ( or “NOT-gate”) Instead of ordinary wires .

Using assignment statements . This statement assigns successive values to the inverse function on the wire .

module top_module(

input in,

output out

);

assign out = ~in;

endmodule

Simulation waveform

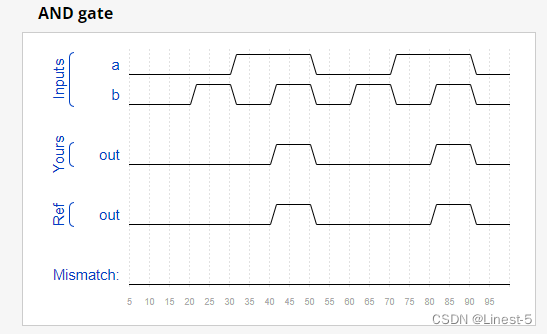

AND gate

Please note that , This circuit NAND gate , Just enter another . If it sounds different , That's because I've begun to describe the signal as being drive ( Having a known value determined by the addition ) Or not by something Driven . Driven by something outside the module . Statement drives the logic level to the wire . As you expected , One line cannot have multiple drivers ( If there is , What is its logical level ?), Lines without drivers will have undefined values ( When synthesizing hardware, it is usually regarded as 0).

module top_module(

input a,

input b,

output out );

assign out = a && b;

endmoduleSimulation waveform

NOR gate

Create an implementation NOR Door module .NOR The gate is output inverted OR Grid . stay Verilog Written in NOR Function requires two operators .

Statements drive wires with values ( or “net”, Because it is more formally called ). This value can be the function you want , As long as it is Combine ( No memory , There is no hidden state ) Function . The sentence is Continuous assignment , Because whenever any input of the output changes , The output will be “ Recalculate ”, Like a simple logic gate .

module top_module(

input a,

input b,

output out );

assign out = ((a==1'b0) && (b==1'b0))?1'b1:1'b0;

endmoduleSimulation waveform

XNOR gate

module top_module(

input a,

input b,

output out );

assign out = ((a==b))?1'b1:1'b0;

endmodule

Simulation waveform

Declaring wires

Create two intermediate wires ( Name whatever you want ) In order to AND and OR The doors are connected . Please note that , Feed NOT The wires of the grid are actually wires , So you don't have to declare the third wire here . Please note that , How wires are made from a source ( Gate output ) drive , But it can supply power to multiple inputs .

module top_module(

input a,

input b,

input c,

input d,

output out,

output out_n );

wire ab;

wire cd;

wire ef;

assign ab = a && b;

assign cd = c && d;

assign ef = ab || cd;

assign out = ef;

assign out_n = !ef;

endmoduleSimulation waveform

7485 chip

7458 It has four AND Door and two OR The chip of the door .

Create with 7458 Modules with the same function of the chip . It has 10 Inputs and 2 Outputs . You can choose to use statements to drive each output wire , You can also choose to declare ( Four ) Wires are used as intermediate signals , Each of the internal wires consists of one AND The output drive of the door .

module top_module (

input p1a, p1b, p1c, p1d, p1e, p1f,

output p1y,

input p2a, p2b, p2c, p2d,

output p2y );

wire wire1;

wire wire2;

wire wire3;

wire wire4;

wire wire5;

wire wire6;

assign wire1 = p2a && p2b;

assign wire2 = p2c && p2d;

assign wire3 = wire1 || wire2;

assign wire4 = p1a && p1c && p1b;

assign wire5 = p1f && p1e && p1d;

assign wire6 = wire4 || wire5;

assign p2y = wire3;

assign p1y = wire6;

endmoduleSimulation waveform

边栏推荐

- 煤炭行业供应链集采系统:数字化推进煤炭产业转型升级

- Guys, do PostgreSQL CDC and PostgreSQL have to configure logical replication? Currently deployed

- C语言编译预处理详情以及宏和函数的对比

- How to write technical documents - this is all my experience

- Kettle [practice 05] four methods, applicable scenarios and advantages and disadvantages analysis of kettle processing JSON format data (cloud resource sharing: JSON data +ktr)

- KUDU1.11 环境安装

- 或许是 WebGIS 下一代的数据规范 - OGC API 系列

- Try to understand the essence of low code platform design from another angle

- 短视频直播系统源码

- 换个姿势做运维!GOPS 2022 · 深圳站精彩内容抢先看!

猜你喜欢

![[postgraduate entrance examination vocabulary training camp] day 8 - complete, traditional, extra, aford, professional, required](/img/e4/81c4ce6f43a3723f5296ed653e9145.png)

[postgraduate entrance examination vocabulary training camp] day 8 - complete, traditional, extra, aford, professional, required

C语言文件操作函数讲解

Kettle【实践 03】水经微图kml类型文件分类解析入库难点细节说明(完整流程实例云资源分享:包含sql+kjb+ktr+测试文件)

JVM堆内存解析

Leetcode-24-exchange nodes in linked list in pairs

UDP 的报文结构和注意事项

安全行业从业者自研开源扫描器合辑

发电机组工作安排问题代码

程序中提升几毫秒、节省几 kB 的内存有必要吗?

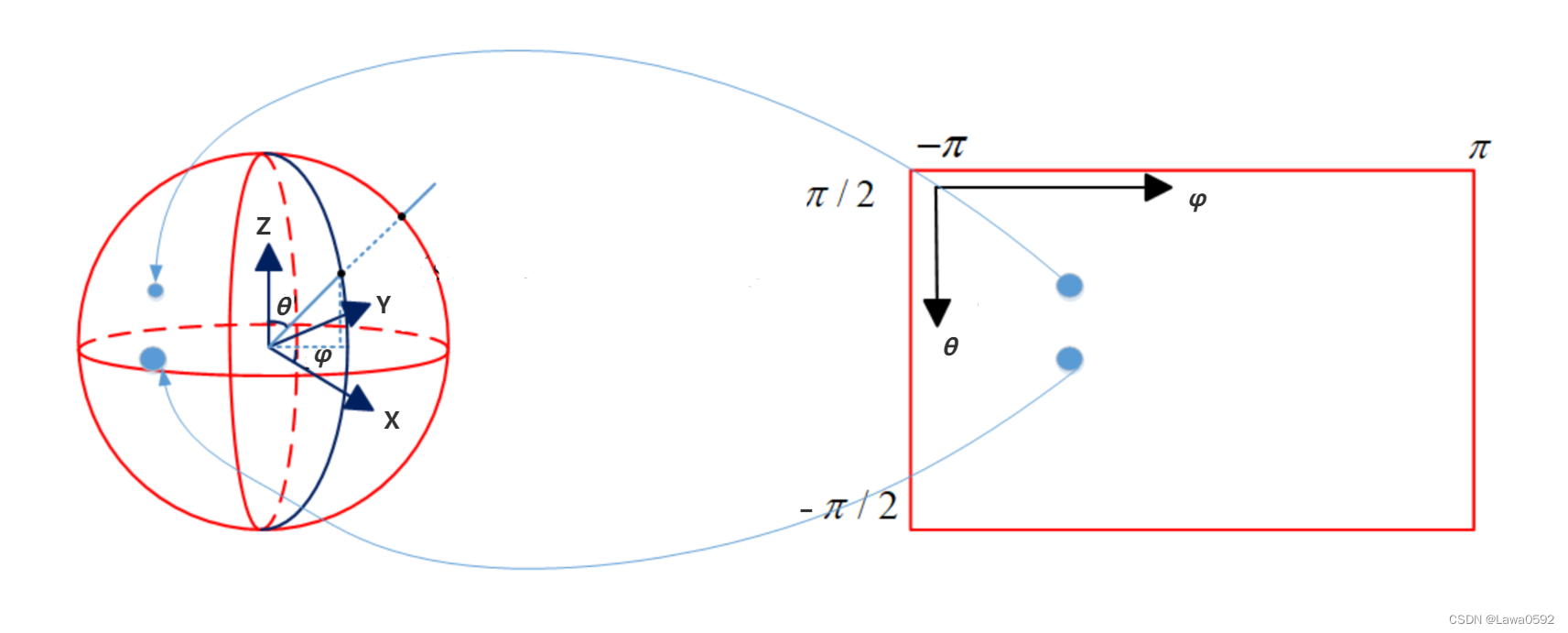

Unity learning notes conversion between plane pixel coordinates of spherical panorama and coordinates on three-dimensional coordinate system

随机推荐

DOM系列之创建元素

【考研词汇训练营】Day 8 —— complete,traditional,extra,afford,professional,require

linux服务器PostgreSQL数据库自动备份

程序中提升几毫秒、节省几 kB 的内存有必要吗?

【HDLBits 刷题】Verilog Language -- Basics 部分

你是为了什么而努力?不放弃才是我们唯一的选择,加油,每一个有缘人

暑假打工 2 个 月,让我明白了 Keepalived 高可用的三种路由方案

[code hoof set novice village question 600] how to change the binary value at the even position of all binaries of a decimal integer to 0

SPSS kmeans clustering practice

After working for two months in the summer vacation, I understood three routing schemes of keepalived high availability

网络层协议 ——— IP协议

pyspark里mapPartitions的用法

SQL语句问题,不知道是否正确,求指导

NepCTF

和外星人如何交流

胸部按摩仪FDA认证注册流程

JVM heap memory parsing

STM32+DHT11读取温湿度数据显示

vite 动态加载静态资源图片,修复打包后图片404问题。

旋转框目标检测mmrotate v0.3.1 训练HRSC2016数据集(二)