当前位置:网站首页>Understand chisel language thoroughly 20. Chisel combinational circuit (II) -- implementation of chisel encoder and decoder

Understand chisel language thoroughly 20. Chisel combinational circuit (II) -- implementation of chisel encoder and decoder

2022-07-20 16:09:00 【github-3rr0r】

Chisel Combinational circuit ( Two )——Chisel Encoder and decoder implementation

The last article talked about Chisel The basic writing method of combinational circuit in , It also introduces Chisel Conditional statement in when/elsewhen/otherwise structure , It should be noted that Chisel The conditional statement block in is not conditional execution , Instead, it corresponds to a multiplexer . In this article, we will use Chisel Realize encoder and decoder , Simultaneous introduction Chisel Medium switch sentence .

decoder (Decoder) Realization

The decoder is used to put a n Bit binary number is decoded into m Circuit of bit signal , among m No more than 2 n 2^n 2n. What we want to achieve here is 2-4 Unique decoder of , It is used to generate the unique heat corresponding to two binary numbers (One-hot) code , There is and only one bit in the single hot code 1, The rest are 0.

The picture below is 2-4 Schematic diagram of the single heat decoder :

If we use the truth table to describe the function of this decoder , The truth table is as follows :

a | b |

|---|---|

| 00 | 0001 |

| 01 | 0010 |

| 10 | 0100 |

| 11 | 1000 |

Of course, we can use what we learned in the last article when Statement to implement :

result := 0.U

when(sel === 0.U) {

result := 1.U

}.elsewhen (sel === 1.U) {

result := 2.U

}.elsewhen (sel === 2.U) {

result := 4.U

}.otherwise {

result := 8.U

}

Although it looks ok , But it's not very simple . because when There is only one signal , Can we have one like other languages switch perhaps case Sentence? ?Chisel China provides switch structure , To use switch The statement first needs to contain chisel3.util package :

import chisel3.util._

And then you can use it switch Statement to describe :

result := 0.U

switch(sel) {

is (0.U) {

result := 1.U}

is (1.U) {

result := 2.U}

is (2.U) {

result := 4.U}

is (3.U) {

result := 8.U}

}

This grammar is also very easy to understand , according to sel Signal to assign different decoded values to result The signal . It should be noted that , Even if we are switch Statement enumerates all possible values ,Chisel This still needs to be assigned a default value , For example, the code above is assigned 0.U to result. But this assignment will not be activated , Therefore, the back-end tools will be optimized . This is done to avoid combinational circuits (Chisel Medium Wire) Incomplete assignment in , Undefined cases will be described in other hardware description languages, such as Verilog Generate unwanted latches in (latch), therefore Chisel Incomplete assignment is not allowed in .

But the above example doesn't seem so easy to understand , Writing decimal values into binary will make the decoder function look clearer . The following is the complete code described in binary :

class Decoder_2_4 extends Module {

val io = IO(new Bundle {

val sel = Input(UInt(2.W))

val result = Output(UInt(4.W))

})

io.result := 0.U

switch(io.sel) {

is("b00".U) {

io.result := "b0001".U}

is("b01".U) {

io.result := "b0010".U}

is("b10".U) {

io.result := "b0100".U}

is("b11".U) {

io.result := "b1000".U}

}

}

This statement looks much clearer , Just like the truth table , Output is as follows :

module Decoder_2_4(

input clock,

input reset,

input [1:0] io_sel,

output [3:0] io_result

);

wire [3:0] _GEN_0 = 2'h3 == io_sel ? 4'h8 : 4'h0; // @[hello.scala 12:15 14:20 18:33]

wire [3:0] _GEN_1 = 2'h2 == io_sel ? 4'h4 : _GEN_0; // @[hello.scala 14:20 17:33]

wire [3:0] _GEN_2 = 2'h1 == io_sel ? 4'h2 : _GEN_1; // @[hello.scala 14:20 16:33]

assign io_result = 2'h0 == io_sel ? 4'h1 : _GEN_2; // @[hello.scala 14:20 15:33]

endmodule

This is actually the case with encoder , But the above code can be simpler . It can be noted that ,0/1/2/3 The corresponding outputs are 0001 Move left 0/1/2/3 position , So we can directly use a basis sel The signal 0001 To achieve , use Chisel Shift operator in << Can be realized :

result := 1.U << sel

Decoder is usually used as building block of multiplexer , Take the output of the decoder as an enable signal , Data input through an and gate as another multiplexer . No, I didn't Chisel There is no need to manually construct a multiplexer , because Mux stay Chisel There are some in the Library . The decoder can also be used for address decoding , Then take the output as the selection signal , For example, different for connecting to the processor IO Selection of equipment .

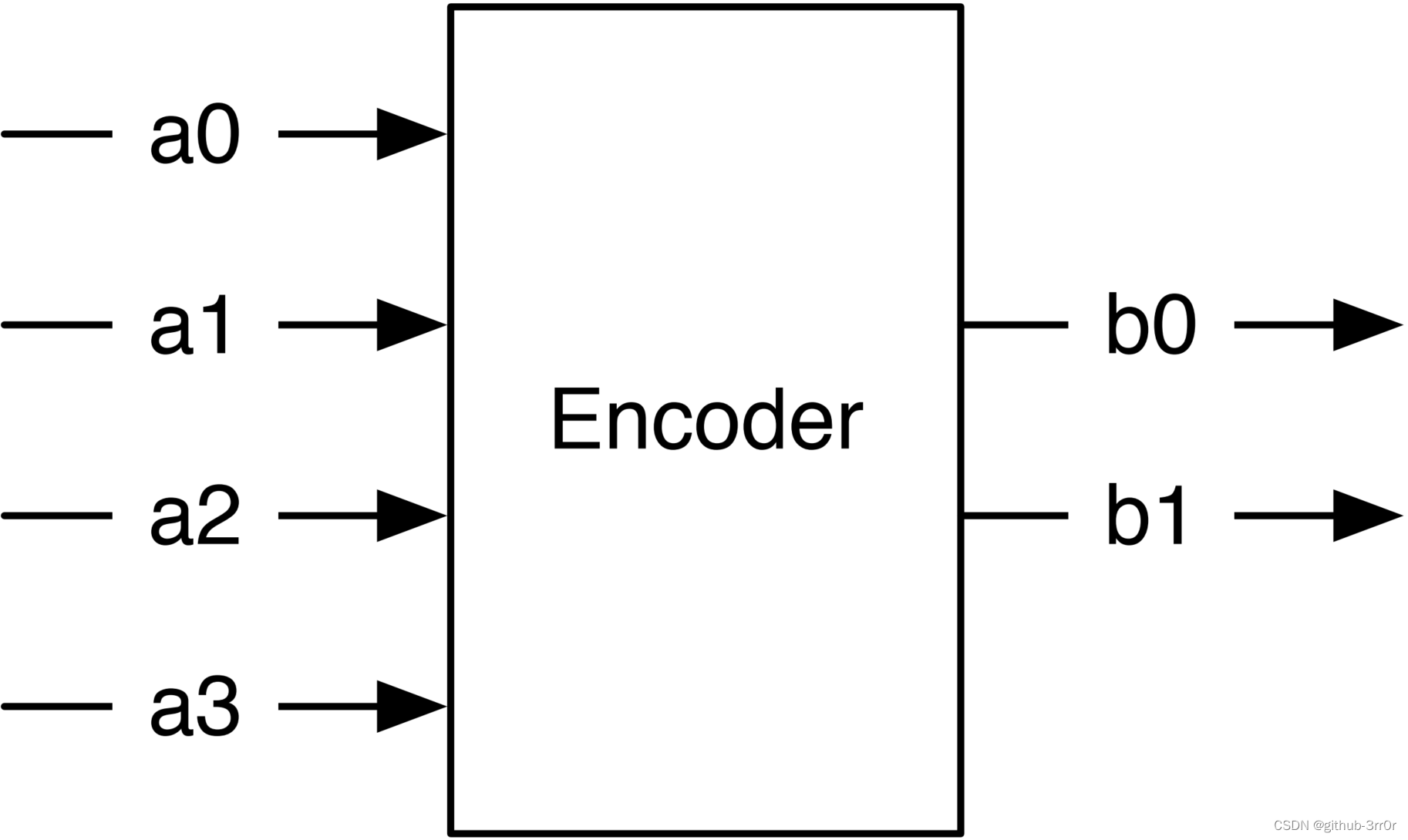

Encoder (Encoder) Realization

The encoder here looks like the decoder in the previous section turned over , That is, the coding circuit from a four bit single hot coding to a two bit binary coding signal . The picture below shows 4-2 Schematic diagram of single heat encoder :

The corresponding truth table is also the reverse of the decoder :

a | b |

|---|---|

| 0001 | 00 |

| 0010 | 01 |

| 0100 | 10 |

| 1000 | 11 |

| ??? | ?? |

The difference is that there is one more line at the bottom , Because the single heat encoder only defines the above four cases , That is, the input must be a unique heat code , For any other input , The output is undefined . Because we can't describe a function with undefined output , We must use the default assignment to capture all undefined input patterns .

Below Chisel The code is assigned a default value 00, And then use switch Statement assignment assigns values to all legal inputs and outputs :

b := "b00".U

switch(a) {

is ("b0001".U) {

b := "b00".U}

is ("b0010".U) {

b := "b01".U}

is ("b0100".U) {

b := "b10".U}

is ("b1000".U) {

b := "b11".U}

}

Conclusion

This article takes decoder and encoder as examples to practice the construction of combinational circuit modules , At the same time, it introduces switch Use of statements . We can also try to write more complex combinational circuits , For example, the code from four bit binary input to seven segment nixie tube code / Decoding function module , It can be further used for 16 Display of hexadecimal digits . In the next part, we will study sequential circuits , Start with the basic register , And then to the counter 、 timer 、 shift register , Finally, memory . End of sequential circuit , The basic content is over , Later, we will introduce higher-level content , Coming soon .

边栏推荐

- 【OpenCV】记录cv2.VideoCapture的一个坑

- 统计信息简介

- uni-app - Refused to display ‘xxx‘ in a frame because an ancestor violates the following Content Sec

- En savoir plus sur le pool de Threads simultanés juc (VIII)

- [ERROR] COLLATION ‘utf8_unicode_ci‘ is not valid for CHARACTER SET ‘latin1‘

- 广州深入开展经营性自建房安全整治“百日行动” 两个月排查房屋逾两百万栋

- How does markdown draw a sequence diagram? One is enough

- PG数据库安装timescale数据库以及备份配置

- PHP step hole array access

- Fiddler设置断点(一)

猜你喜欢

Heartless sword English translation of Wu Fei's song of longitude and latitude

![[development of large-scale e-commerce projects] mall business - Search Service - building page environment -47](/img/3a/7f99c01518ae91779713b6ded6f22b.png)

[development of large-scale e-commerce projects] mall business - Search Service - building page environment -47

使用 GPU 发现人脑连接,大规模 GPU 实现了 100 倍的加速

【大型电商项目开发】缓存-分布式锁-缓存一致性解决-45

En savoir plus sur le pool de Threads simultanés juc (VIII)

原来何恺明提出的MAE还是一种数据增强!上交&华为基于MAE提出掩蔽重建数据增强,优于CutMix、Cutout和Mixup!...

Linux 编译安装redis 离线

获取疫情资讯数据

Which is the best test management tool?

深入了解JUC并发(七)常用的辅助类

随机推荐

atos比例溢流阀AGMZO-TERS-PS-010/315

Markdown如何画时序图,一篇就够了

吃透Chisel语言.20.Chisel组合电路(二)——Chisel编码器与解码器实现

Linux 编译安装redis 离线

PHP step hole array access

BI技巧丨同环比计算

原来何恺明提出的MAE还是一种数据增强!上交&华为基于MAE提出掩蔽重建数据增强,优于CutMix、Cutout和Mixup!...

Don't understand MySQL database? Alibaba P8 architects will show you MySQL and Optimization in simple terms

Era journey of operators: plant 5.5G magic beans and climb the Digital Sky Garden

Spark高效数据分析03、Spack SQL

ES6 -- iterator, basic use of generator

微信小程序获取----onenet的数据并控制stm32的板载LED

走进首个通用无代码开发平台—iVX

测试--基础知识篇

吃透Chisel语言.15.Chisel模块详解(二)——Chisel模块嵌套和ALU实现

En savoir plus sur le pool de Threads simultanés juc (VIII)

Study notes - C string delete character

php 踩坑 数组访问

数据科学与计算智能:内涵、范式与机遇

吃透Chisel语言.16.Chisel模块详解(三)——Chisel的整体连接(Bulk Connection),以流水线处理器为例