当前位置:网站首页>Why is risc-v architecture gaining momentum

Why is risc-v architecture gaining momentum

2022-07-22 13:02:00 【Binary star】

Catalog

Related references :

RISC-V Related progress

Basic concepts

Instruction set : A set of instructions , Instructions are the smallest unit of the processor

Instruction set architecture : The intermediate abstraction layer between the underlying hardware of the processor and the software running on it , Including data types 、 The storage model 、 Processor status visible to software 、 Instruction set 、 Instruction model and external interface

Microarchitecture : The specific hardware implementation scheme of the processor

CISC: Complex instruction set architecture , Contains commonly used and infrequently used instructions of the processor , There are many instructions

RISC: Reduced instruction set architecture , For less commonly used operations , By executing the combination of several common instructions , The number of instructions is relatively small

32 Bit and 64 position : The number of bits in the processor instruction set architecture , Generally refers to the width of general-purpose registers

Development track

History first :RISC-V The architecture is mainly developed by the University of California, Berkeley Krste Asanovic professor 、Andrew Waterman and Yunsup Lee Wait for developers to 2010 The invention of , And got the leader of computer architecture David Patterson Strong support . Based on the problems of the previous architecture ,RISC-V Architecture was born .2016 year ,RISC-V The foundation was officially established and began to operate , It is a non-profit organization , Responsible for maintaining standards RISC-V Instruction set manual and architecture documentation , And push RISC-V The development of Architecture .

RISC-V Architecture goal : Become a completely open instruction set , It can be freely used by any academic institution or business organization ; Become a standard instruction set that is really suitable for hardware implementation and stable .

RISC-V Instruction set architecture features :

- A modular subset of instructions :

RISC-VThe instruction set of is organized in a modular way , Each module is represented by an English letter (Volume 1, Unprivileged Spec v. 20191213Directory visible ) - Configurable general purpose register set : Support 32 position /64 An architecture , Use separate integer general-purpose registers and floating-point register sets

- Regular instruction coding : Regular coding , The index of the general register set required by the instruction is placed in a fixed position

- Simple memory access instructions : And

RISCThe architecture is similar , Use onlyLOADandSTOREInstruction access memory , - Efficient branch jump instructions : Use conditional jump instructions , No need to use the status register ; about

CPUTo determine whether to use different branch predictions , By default, static branch prediction technology is used - Simple subroutine calls : The information saved when the subroutine is called is placed in the Public Library

- Unconditional code execution :

RISC-VFor any conditional judgment, use ordinary conditional branch jump instructions - No branch delay slot :

MIPSThis usage is often used in architecture , But it will make the hardware design complex - Zero overhead hardware loop : Use self increasing or self decreasing instead

- Simple operation instructions : For operation exceptions , The hardware will only return a default value , Leave the rest to the software

- Compress a subset of instructions

- Privilege mode : Machine mode 、 Supervision mode 、 User mode

- CSR register : Control and status registers

- Interrupts and exceptions

- Vector instruction subset

- Custom instruction extensions : Support for third party expansion

All in all ,RISC-V Generally, it revolves in one direction : Reduce hardware pressure .

common RISC-V Commercial version and open source version :Rocket Core、BOOM Core、Freedom SoC、LowRISC SoC、PULPino Core and SoC、PicoRV32 Core、SCR1 Core、ORCA Core、Andes Core、Microsemi Core……

边栏推荐

- What are the advantages of WMS warehouse management system based on bar code

- Alibaba cloud technology expert Yang Zeqiang: building observable capabilities on elastic computing cloud

- 技术人员突然离职,如何接手他的项目?

- 不同实现方式的球幕投影都有哪些特点

- 97 page digital twin enabled smart Park IOT cloud platform construction scheme

- IOInputStream类型

- 《六》BFC

- priority_queue删除

- B端产品经理学习:导入模板设计

- Selenium启动chrome,页面显示与隐藏事件

猜你喜欢

Format data JSON in pycharm tool

![[recommended collection] handling method of cache avalanche](/img/d8/a367c26b51d9dbaf53bf4fe2a13917.png)

[recommended collection] handling method of cache avalanche

Redis core principles

![[高数] 用定义证明 a 的 1/n 次幂的极限为 1](/img/84/034a115eab8ef439615287b6fe63c4.jpg)

[高数] 用定义证明 a 的 1/n 次幂的极限为 1

![[PHP environment setup /wamp/ interpreter / download]](/img/e8/87f923186c60f1614bc3ee60b9159f.png)

[PHP environment setup /wamp/ interpreter / download]

Detailed explanation of C language pointer

Wechat hotel reservation applet graduation design (2) applet function

![[2022 national games simulation] minimum spanning tree - Kruskal, matrix, tree section dynamic DP](/img/c8/0f6e6451197524a7214bb0193acb69.png)

[2022 national games simulation] minimum spanning tree - Kruskal, matrix, tree section dynamic DP

华为无线设备配置攻击检测功能

esp8266模拟输入(ADC)检测问题

随机推荐

Optimization of deep recursion

Multiple backpack notes

[technology] introduction of uniapp u-charts partial demo

点绕网格中心顺时针旋转 90° 180° 270°坐标的变化

The graduation project of wechat hotel reservation applet (1) development outline

What are the advantages of WMS warehouse management system based on bar code

线程池配置 异步编排 CompletableFuture

Wechat hotel reservation applet graduation design (2) applet function

深层递归的优化

Working principle of Brushless DC motor

What is the role of software compatibility testing? Necessary testing tools for compatibility testing

Thread pool configuration asynchronous orchestration completable future

ECCV 2022 | the role of shape, texture and color in visual recognition

C # split string by string

使用JDBC操作数据库数据库操作

数据中台建设模式的4大趋势和3大重点总结全了

小程序毕设作品之微信酒店预订小程序毕业设计(3)后台功能

如何使用多类型数据预训练多模态模型?

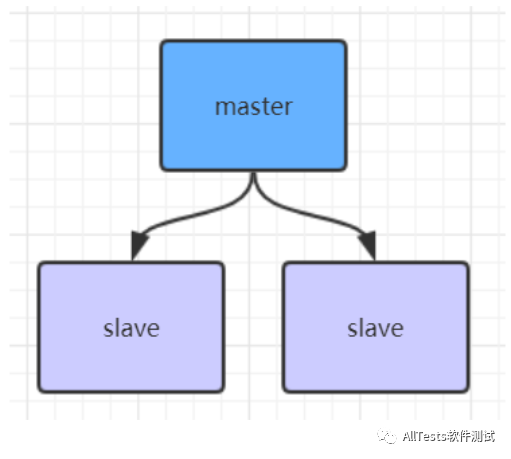

4种 Redis 集群方案及优缺点对比

threejs